Making transistor circuits more robust in power electronics

Fast IGBTs (insulated gate bipolar transistors) have so far been the last word in power electronics, providing the best of both worlds in FETs (field-effect transistors) on the input with bipolar transistors on the collector-emitter path.

SiC (silicon carbide) FETs have meanwhile been seeing increasing use in more demanding applications, as they allow higher switching frequencies while reducing switching losses. But both technologies have one thing in common: they need optimal control and connections to provide years of reliable service under possibly harsh conditions, so false triggering must be avoided at all costs.

IGBTs contain monocrystalline silicon and are generally considered to be a cost-effective standard solution, whereas SiC FETs use silicon carbide to allow higher junction temperatures and thinner insulation layers on the gate to improve thermal conductivity and power density. Switching losses in SiC FETs are at least four times lower than in IGBTs (Figure 1). In particular, SiC FETs eliminate the current tail typical of IGBTs on switching off — an advantage that especially pays off in the high-performance range and higher switching frequencies, allowing a noticeable increase in efficiency from using SiC FETs in bridge circuits, for example. Alternatively, increasing the switching frequency at constant efficiency can save cost and weight in passive components, especially in inductances. Being more expensive, SiC FETs are more commonly found in demanding tasks; IGBTs dominate the mass market.

Preventing false triggering

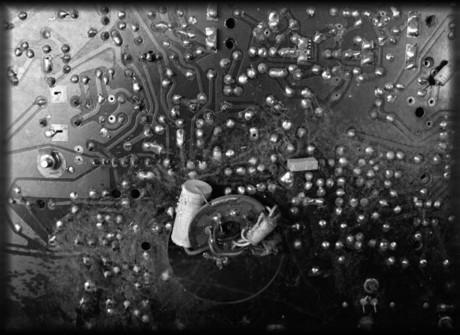

Assessing robustness in IGBT and SiC FET circuits quickly involves the risk of focusing too much on the transistor specifications while neglecting the driver module and circuit layout; as so often in analog engineering, the devil is in the detail — that is, parasitic components not shown in any circuit diagram. To illustrate the issues facing developers in real life, we have included parasitic capacitances and inductances that play a role in IGBTs and SiC FETs in a simple block diagram and marked them green (Figure 2).

The circuit must be dimensioned to avoid false triggering in extreme situations. Sporadic short circuits in a component such as a bridge circuit would cause EMC problems and reduce the component’s service life, or possibly even cause its complete destruction.

Preventing this involves dealing with the two major causes for false triggering:

- Impact of parasitic capacitances such as Creverse (Miller capacitance) and Cinput

- Impact of parasitic r inductances such as Lgate and Lemitter

Cause 1

Creverse needs to be charged if collector-emitter voltage increases during off operations in the IGBT. The charging current can be estimated to a degree using the following formula:

ICreverse = CReverse x dUCE/dt

Note that Creverse strongly depends on not only voltage, but also temperature and current. It makes sense to take measurements in real-life conditions as this value is insufficiently defined in most data sheets.

- Charging Creverse is not the actual problem, however — the actual problem arises when the charging current causes Miller capacitance, input capacitance Cinput has been charged far enough to reach or exceed threshold voltage (Figure 3).

The Cinput charging current can be defined as follows:

ICinput = ICreverse – IDriver

Idriver depends on gate resistances, and also Lgate in dynamic operation. The latter depends on circuit layout and the package used.

This yields a series of parameters that can be tweaked to keep Miller capacitance from causing false triggers:

- Limit dUCE/dt to flatten the switching ramps and ICreverse curve. However, this will unfortunately also increase switching losses as a side effect.

- Reduce parasitic inductance Lgate by optimising the circuitry, thus reducing the voltage rise at the gate.

- Use a negative n gate-emitter voltage to widen the safety margin up to the threshold voltage.

The last solution is the most elegant.

Cause 2

When switched on, the load current flows through the transistor, and therefore also through the emitter inductance. Breaking the current will cause negative voltage at Lemitter according to the following formula:

-U= Lemitter x dI/dt

This will bring the emitter voltage to below GND. However, the driver takes the gate down to GND, resulting in a positive gate-emitter voltage. Exceeding the threshold voltage will cause a false trigger, switching the transistor on.

Parasitic inductances from other bridge branches and the circuit need to be included in designing bridge circuits. Not insulating the driver circuit will result in power GND and driver GND having a significant impact on parasitic inductances, and therefore also the risk of false triggering in a bridge. This article cannot cover every conceivable bridge design, so we recommend downloading the white paper ‘Designing Robust Transistor Circuits with IGBTs and SIC MOSFETs’ from www.recom-power.com/papers for further details.

How to minimise the impact of parasitic inductances:

- Cut dI/dt as slower drops in current will reduce the voltage induced between the gate and emitter. However, this will also increase switching losses.

- Reduce circuit inductances. The shorter the conductors, the lower the parasitic voltages.

- Use a negative gate-emitter voltage to widen the safety margin to the gate-emitter threshold voltage.

- Use galvanically isolated gate drivers and isolated DC/DC converters. Connecting the driver supply connected directly to the respective emitters will largely eliminate the impact of circuit inductance.

- Use drivers with separate connections for the control emitter (Kelvin contact). This may also cause parasitic inductance, but it will not flow through the load current and cause any significant issues.

Measuring circuit robustness

Reliably measuring IGBT and SiC FET parameters is anything but trivial. Parasitic inductances Lgate and Lemitter prevent a direct path to the gate and emitter, rendering reliable measurement of the safety margin to the gate-emitter voltage threshold impossible during dynamic operation; this again confirms the old rule of garbage in, garbage out.

One solution would be to measure cross-current on the bridge, although care does need to be taken to avoid additional resistances or capacitances in the gate-emitter circuit that would alter switching behaviour in IGBTs or SiC FETs. One tried and true measurement method crosses a current shunt upstream from the high-side collector via voltage drop; this requires an oscilloscope with isolated inputs and a corresponding probe.

A reading free of suspicious current will not guarantee freedom from false triggering in the series, however. First, gate-emitter threshold voltages vary widely between individual transistors of the same type; and second, junction temperature plays a significant role (Figure 4). Bulletproof reliability would require transistors with minimum threshold voltage as seen on the diagram, which would need to be measured at the maximum permissible temperature and greatest possible dI/dt and dv/dt.

Isolated DC/DC converters ensure optimised power supply

As mentioned at the outset, switching losses are mainly determined by control quality so gate drivers and their supply require special attention. The drivers are directly coupled to the high potential of the transistors, so both the input signal and the power supply to driver ICs need to be thoroughly insulated. Isolated DC/DC converters provide a very convenient solution.

The driver modules on the market are asymmetrically controlled with positive and negative voltages; IGBT and SiC FET drivers differ in the voltages required.

Data sheets specify voltages between 3 and 6 V for IGBTs; these can decrease to 1 to 2 V with increasing junction temperature. Values of 15 V have become established for fast triggering in real-life applications.

Preventing false triggering despite steep ramps during switching requires negative offset voltage on the gate, as described above. Values of -9 V have proven safe in practice. This is why dual isolated DC/DC converters with asymmetric voltages at 15 and -9 V have turned out to be especially suitable in supplying IGBT drivers.

Threshold voltages on SiC FETs are significantly lower than on IGBTs, and also decrease with increasing temperature. This would lead to the logical conclusion that SiC FETs also require more negative offset voltage on the gate. In contrast, studies conducted at the University of Nottingham suggest that the gate oxide changes to a varying degree throughout the lifetime of the transistor.

Threshold voltage decreases by around 0.2 to 0.3 V over a lifetime of a thousand hours, and then remains stable at gate source voltage of -5 V. The change is around five times that at UGS= -10 V, and the variation between transistors is so high that some SiC FETs were already ‘normal on’ at 0 V. This resulted in the recommendation not to use gate offset voltage values more negative than -5 V.

A positive voltage of +15 V would be theoretically possible as on an IGBT; the threshold voltage is substantially lower, ensuring reliable switching behaviour in SiC FETs. However, the output characteristics at different gate source voltages have demonstrated that higher gate source voltages would achieve a substantially lower rds(on) (Figure 5). A gate-source voltage of +20 V makes the most of a SiC FET’s benefits, so an isolated DC/DC converter running at +20/-5 V is the best choice for supplying the driver.

Particular attention should be given to the insulation resistance of the DC/DC converter; high switching frequencies — usually 10 to 50 kHz in IGBTs, and more than 50 kHz in SiC FETs — and steep ramps subject the insulation barrier to constant stress. Spikes are often significantly higher than an oscilloscope can catch. Relying on measurement alone and using a converter on insulation that is too tightly dimensioned as it is risks long-term reliability in the system, so developers tend to allow for sufficient safety reserves and use converters with the best possible insulation when dimensioning fast power switches.

A complete line of isolated DC/DC converters for IGBT and SiC FET applications

Power module manufacturer RECOM has developed a complete family of DC/DC converters specifically designed for supplying IGBT and SiC FET drivers.

The converters have asymmetric outputs at either +15/-9 V for IGBTs or +20/-5 V for SiC FETs, and are available at input voltages of 5, 12, 15 and 24 V. The power required significantly depends on the switching frequency of the system; values of 1 W are mostly enough for frequencies up to 10 kHz, whereas frequencies of 50 kHz and more require up to 2 W. The products run in power-sharing mode, which means that the rated power can be distributed over the two outlets.

There are other differences in insulation; products in the RKZ family are available at insulation voltages of 3 and 4 kVDC, with RxxP2xx versions as high as 5.2 kVDC.

RECOM subjects all newly developed converters to intensive HALT (highly accelerated long time) tests in its in-house environmental laboratory to ensure long service lives even under extreme conditions. The guarantee lasts three years. All converters are manufactured according to the RoHS2 and Reach directive, are certified according to UL 60950-1 and can be sampled by all major distributors.

Hidden semiconductor activity spotted by researchers

Researchers have discovered that the material that a semiconductor chip device is built on,...

3D reflectors help boost data rate in wireless communications

Cornell researchers have developed a semiconductor chip that will enable smaller devices to...

Scientists revolutionise wireless communication with 3D processors

Scientists have developed a method for using semiconductor technology to manufacture processors...