# DCM™ Design Guide

# **Table of Contents**

| 1. Introduction to the DCM Product Line                                     | 4  |

|-----------------------------------------------------------------------------|----|

| Introduction to DC-DC converter Module (DCM)                                | 4  |

| Useful Links                                                                | 5  |

| 2. Design Requirements                                                      | 6  |

| Safety Considerations                                                       | 7  |

| DCM Output Capacitor                                                        | 10 |

| Location of Output Capacitor                                                | 10 |

| Referencing of Input and Output Terminals                                   | 10 |

| Filtering Guidelines Introduction                                           | 11 |

| Source Impedance and its Effects on Performance of the Switching Converters | 12 |

| Negative Incremental Input Impedance (Z <sub>IN-DCM</sub> )                 | 13 |

| Stability Analysis                                                          | 13 |

| Optimum Value of Decoupling Capacitor                                       | 15 |

| Stability Analysis of a Multiple Converter System                           | 18 |

| Input Filter Design and Simulation                                          | 21 |

| Problems Associated with Addition of Input Filters:                         | 21 |

| Input Filter Design                                                         | 22 |

| Undamped LC Filter Network                                                  | 24 |

| Parallel-Damped Filter Network                                              | 26 |

| Simplified Parallel-Damping Network                                         | 29 |

| Series-Damped Filter Network                                                | 29 |

| Simplified Series-Damping Filter Network                                    | 32 |

| Application of Filters for Differential-Mode Noise Reduction                | 34 |

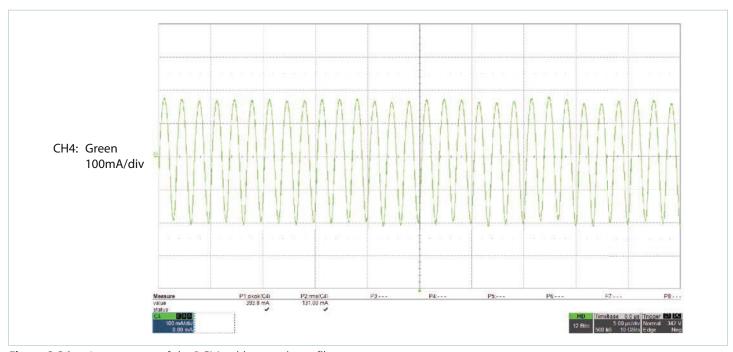

| Measurement of Input Currents without an Input Filter                       | 34 |

| Measurement of Input Currents with a Parallel-Damped Input Filter           | 35 |

| Common-Mode Input Filter Design                                             | 36 |

| Noise Mitigation Techniques                                                 | 37 |

| Common-Mode Noise Filter Design Steps                                       | 37 |

| 3. Operation of the DCM                                                     | 38 |

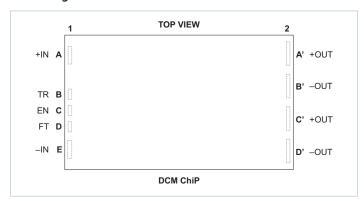

| Pin Configuration                                                           | 38 |

| Control Pin Functions                                                       | 38 |

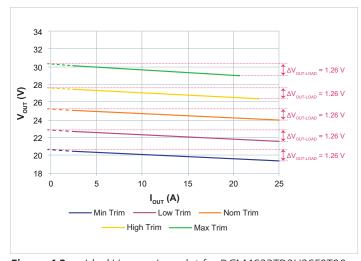

| Output Voltage Trimming (TR Pin) (Applies to all DCM Series)                | 39 |

| TR Pin Considerations                                                       | 39 |

| Enable / Disable Control (EN Pin)                                           | 40 |

| DCMxxxxxxxxxxx00 and DCMxxxxxxxxxxx70 Series                                | 40 |

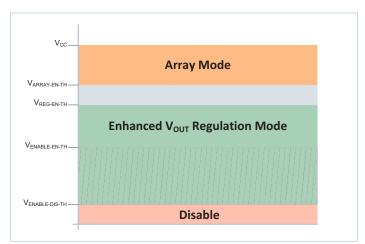

| DCMxxxxxxxxxxx60 Series                                                     | 40 |

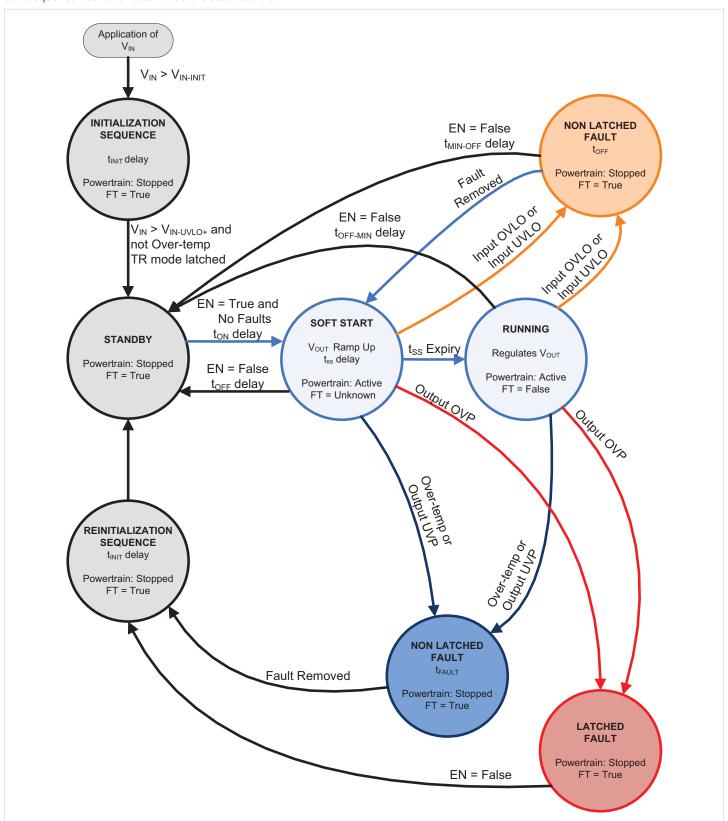

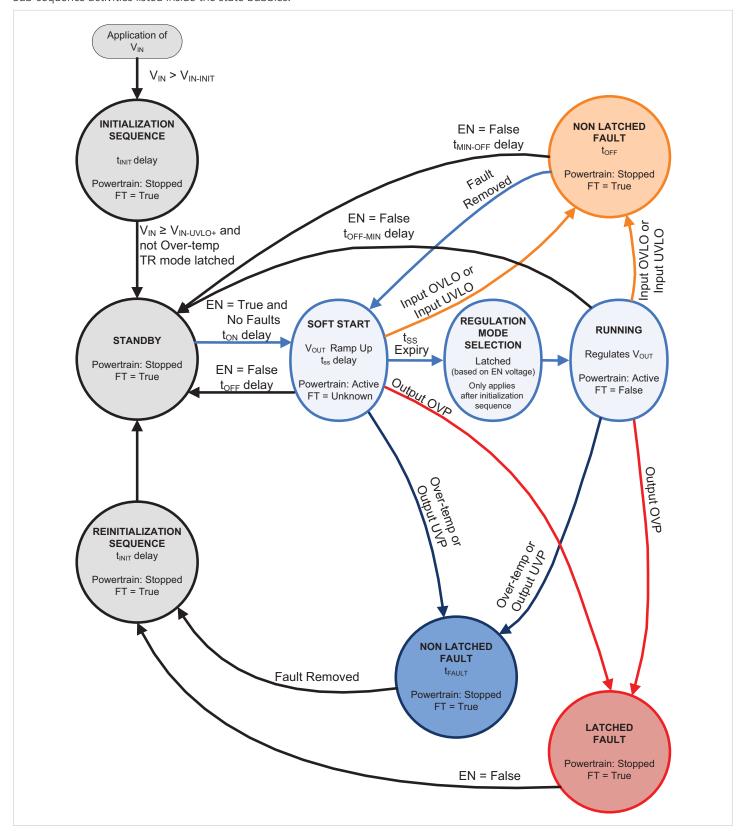

|              | ligh-Level Functional State Diagram CMxxxxxxxxxxx00 and DCMxxxxxxxxxx70 Series Only                           | 42        |

|--------------|---------------------------------------------------------------------------------------------------------------|-----------|

|              | ligh-Level Functional State Diagram CMxxxxxxxxxxx60 Series Only                                               | 43        |

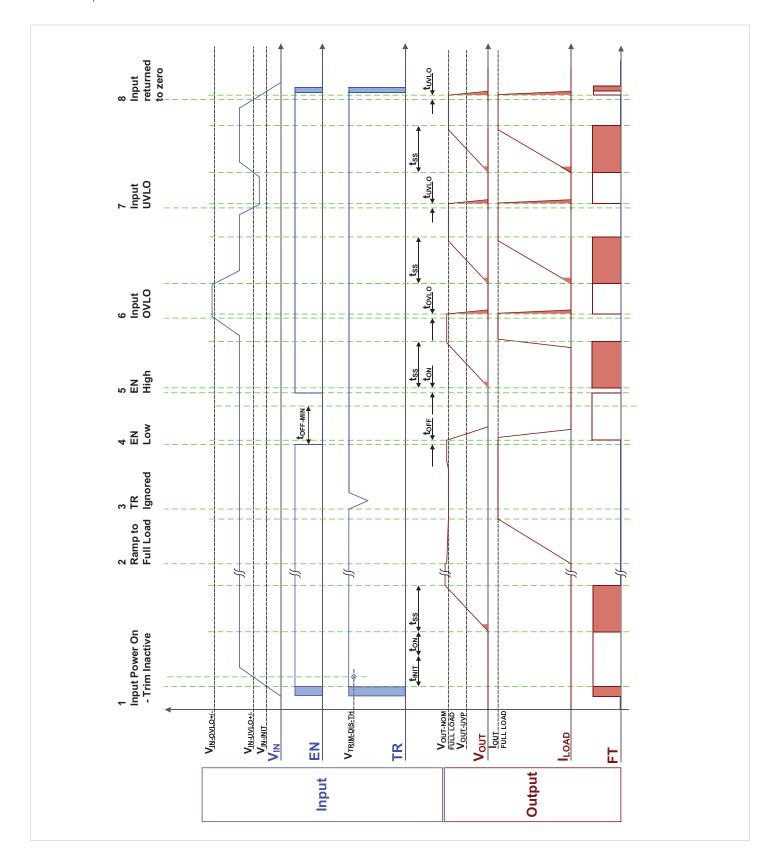

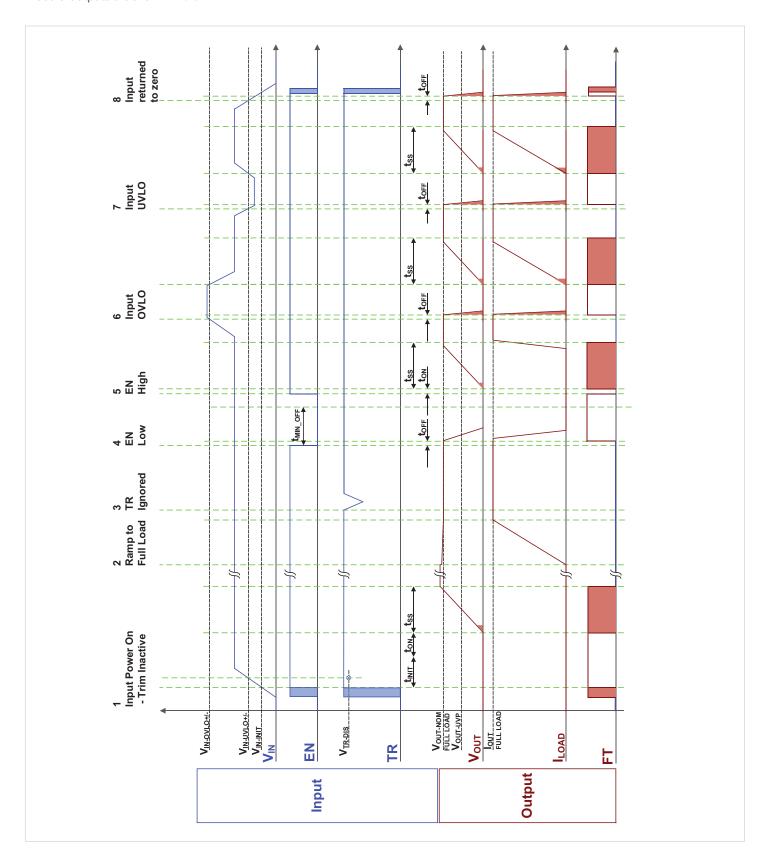

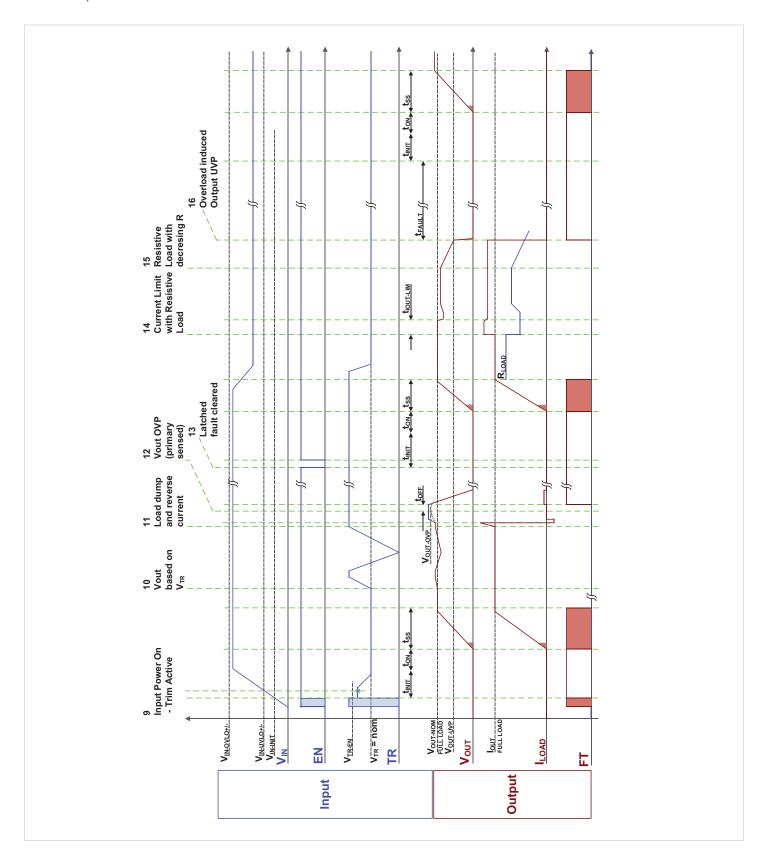

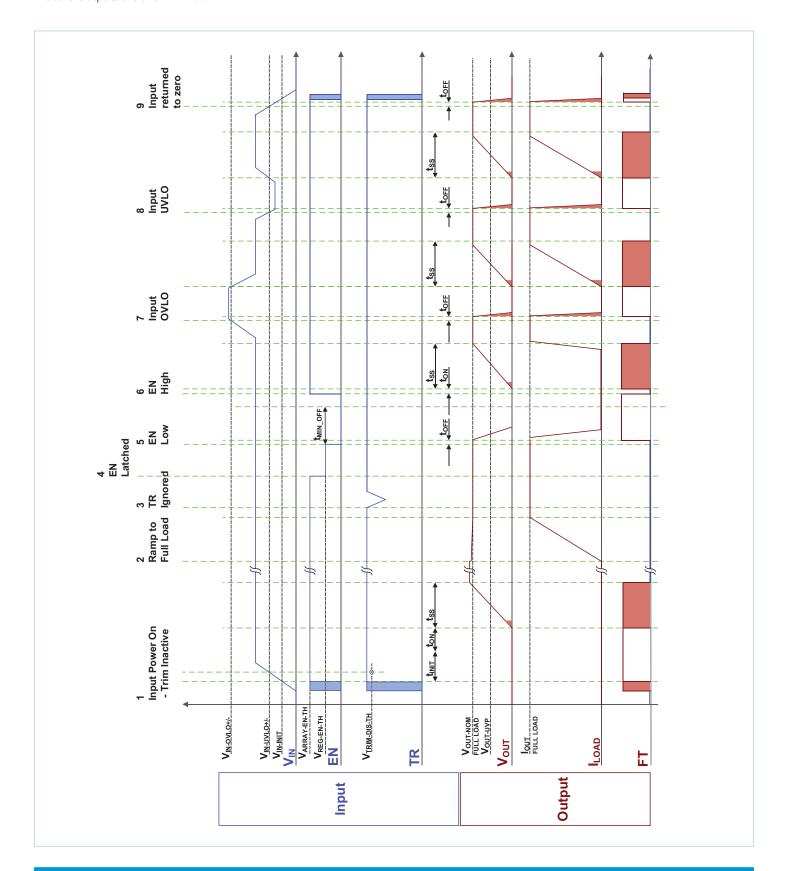

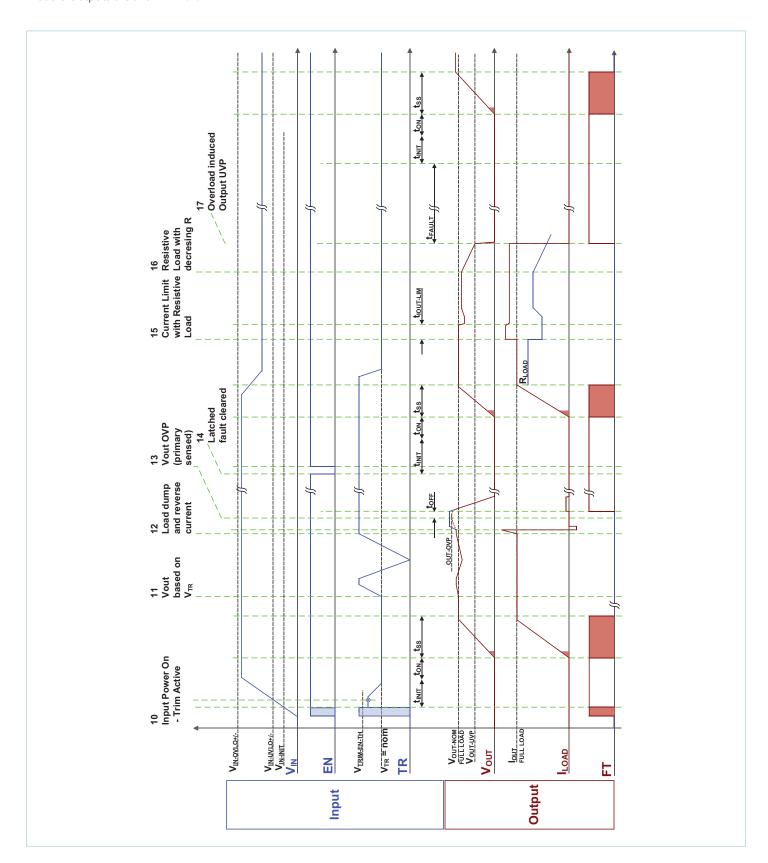

| I            | iming Diagrams: DCMxxxxxxxxxxx00 Series                                                                       | 44        |

| I            | iming Diagrams: DCMxxxxxxxxxxx70 Series                                                                       | 46        |

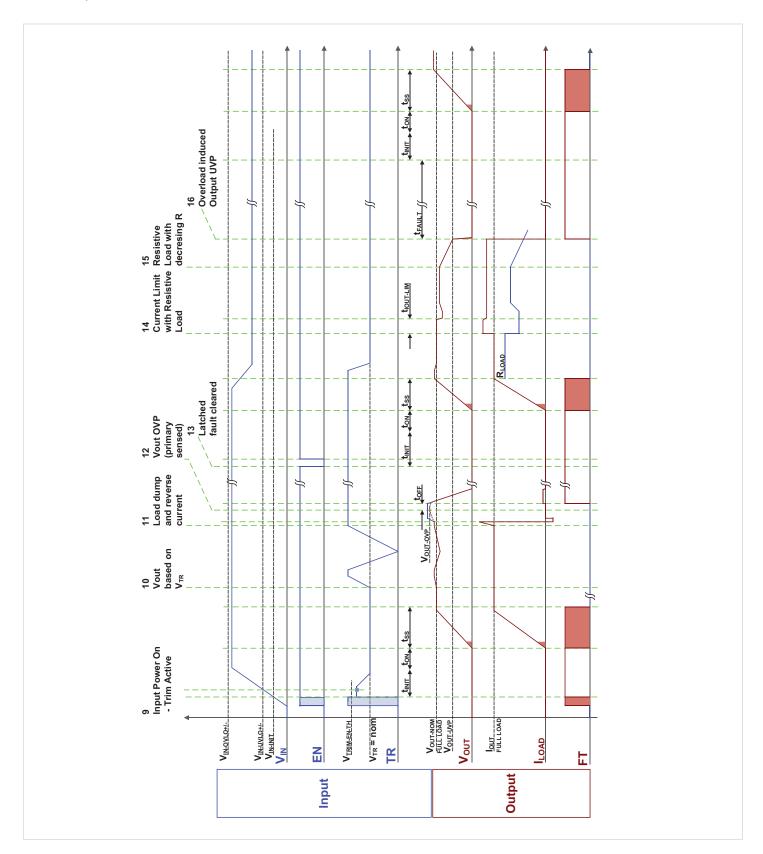

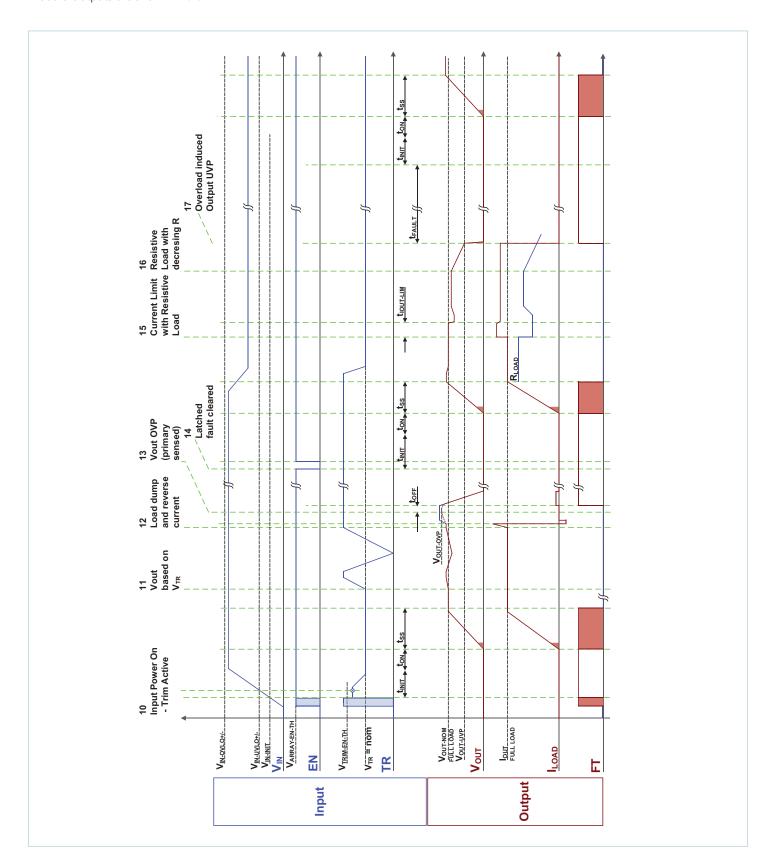

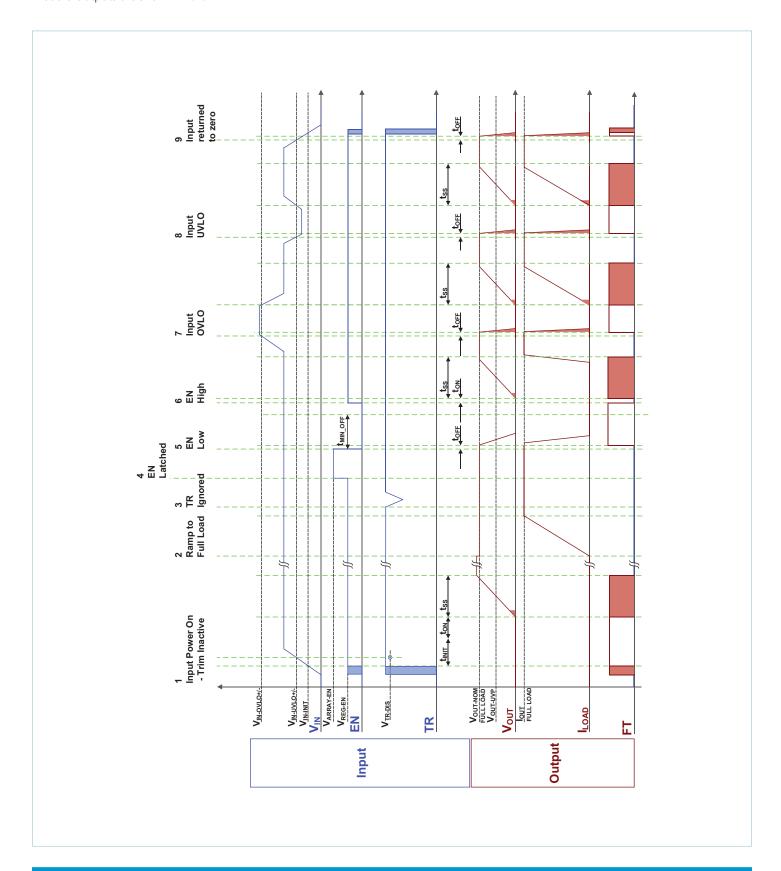

|              | iming Diagrams: DCMxxxxxxxxxxx60 Series:<br>rray Mode                                                         | 48        |

|              | iming Diagrams: DCMxxxxxxxxxxx60 Series:<br>nhanced V <sub>OUT</sub> Regulation Mode                          | <u>50</u> |

|              | tart-Up Process_<br>Applies to all DCM Series)                                                                | <u>52</u> |

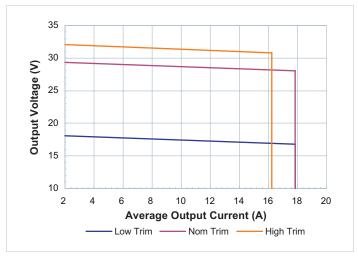

| (/           | lominal Output Voltage Load Line<br>Applies to DCMxxxxxxxxxxx00 and<br>CMxxxxxxxxxxx60 in Array Mode)         | 52        |

| (/           | lominal Output Voltage Temperature Coefficient Applies to DCMxxxxxxxxxxx00 and CMxxxxxxxxxxx60 in Array Mode) | <u>52</u> |

|              | ight-Load Boosting_<br>Applies to all DCM Series)                                                             | 53        |

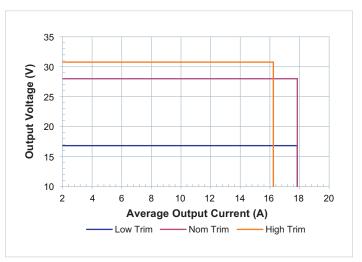

| <u>O</u>     | Overall Output Voltage Transfer Function                                                                      | 53        |

|              | CMxxxxxxxxxxx00 and DCMxxxxxxxxxxx60 series  Array Mode                                                       | 53        |

|              | CMxxxxxxxxxxx70 and DCMxxxxxxxxxxx60 series<br>n Enhanced V <sub>OUT</sub> . Regulation Mode                  | <u>53</u> |

|              | ault Handling<br>Applies to all DCM Series)                                                                   | <u>54</u> |

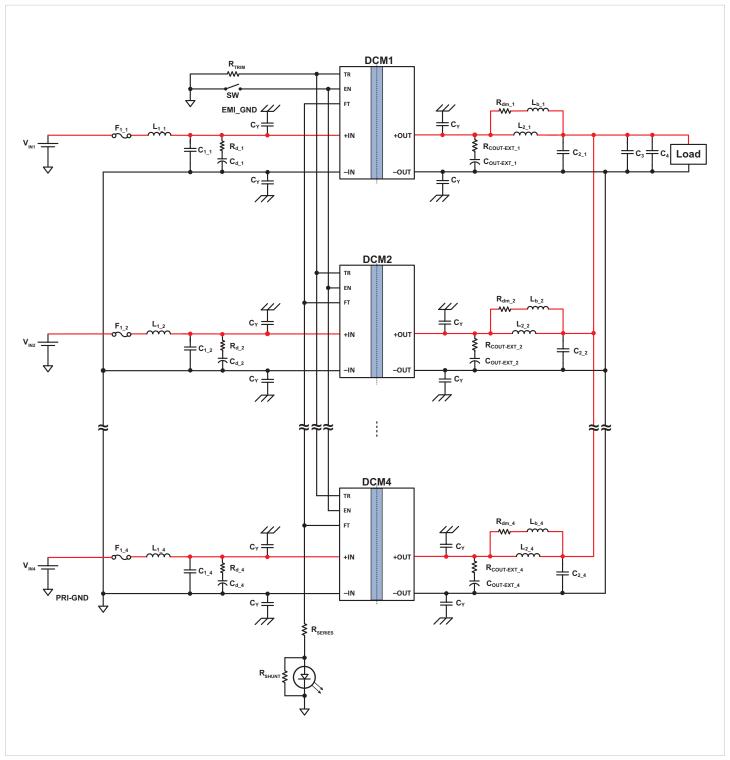

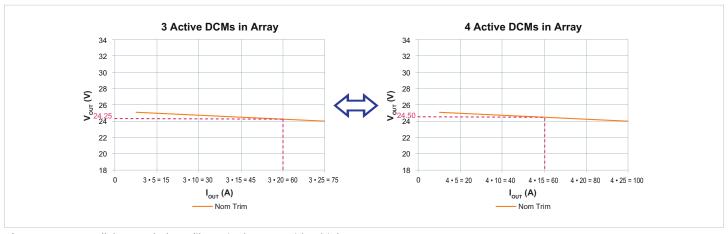

| <u>4. Pa</u> | rallel Operation                                                                                              | <u>55</u> |

| 0            | Overall Output Voltage Transfer Function                                                                      | <u>55</u> |

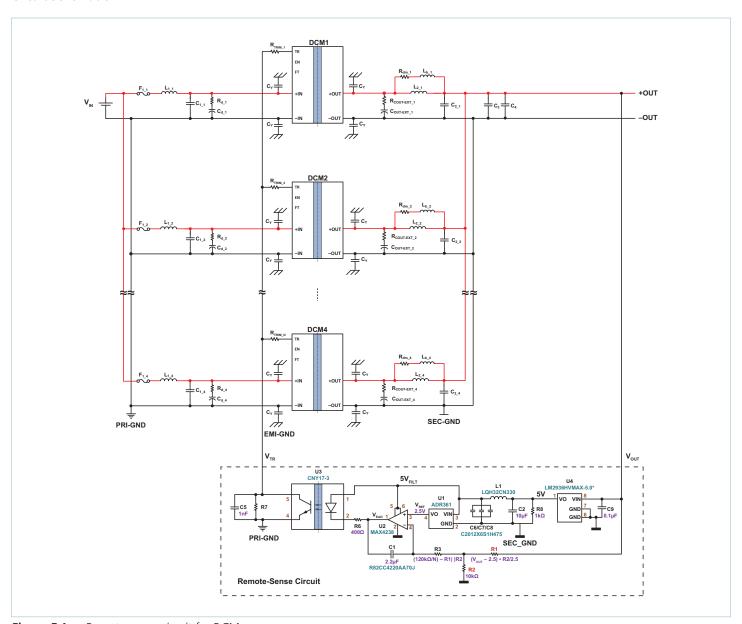

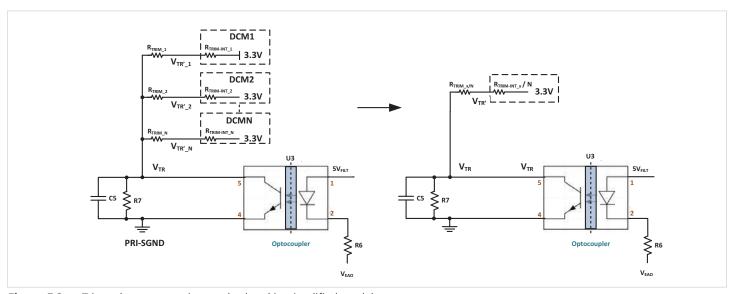

| <u>S</u>     | ample Circuit                                                                                                 | <u>55</u> |

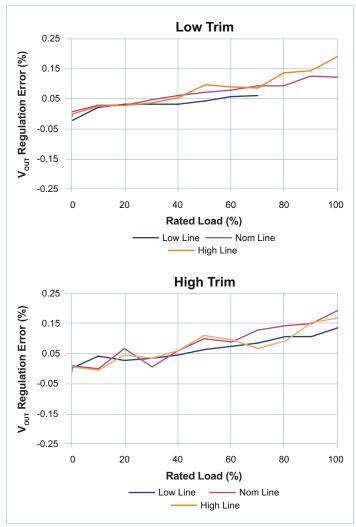

| <u>O</u>     | Output Voltage Regulation                                                                                     | 57        |

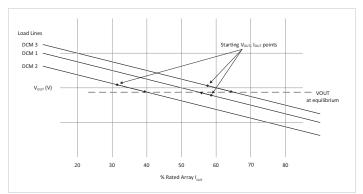

| Lo           | oad Sharing                                                                                                   | 57        |

| <u>S</u> †   | tart Up                                                                                                       | <u>59</u> |

|              | pecial Application: Optimizing Current Sharing at<br>ligh Temperature                                         | <u>59</u> |

| <u>S</u>     | pecial Application: Non-Equal Trim Levels                                                                     | 60        |

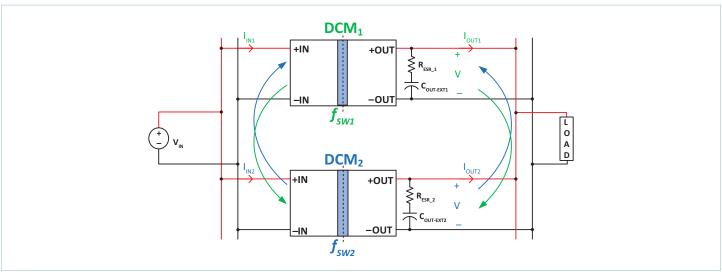

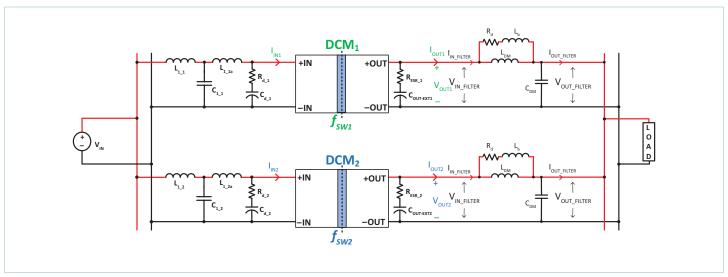

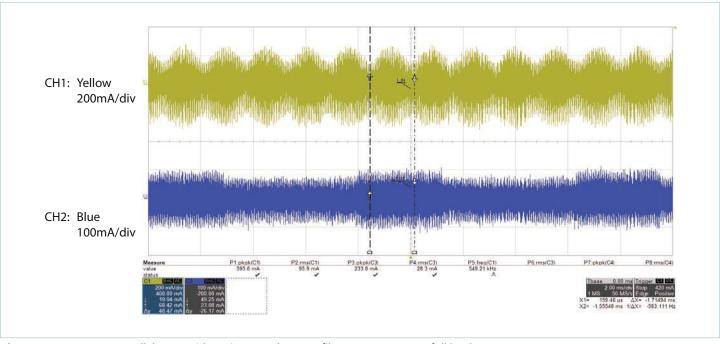

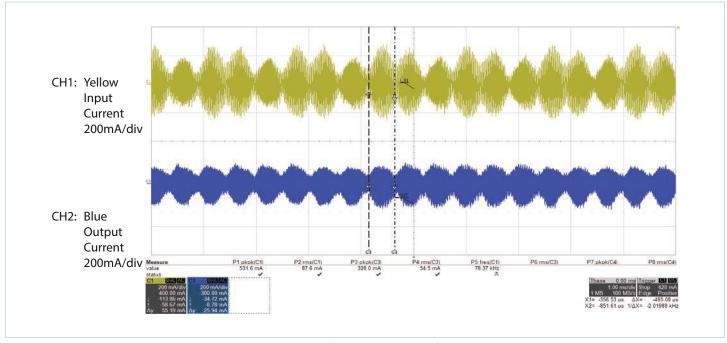

|              | roblem Associated with the Parallel Operation of PC-DC Converter Modules                                      | 60        |

|              | resign Guidelines for Suppressing Beat Frequency<br>Oscillations and Feedback Control Loop Interactions       | 61        |

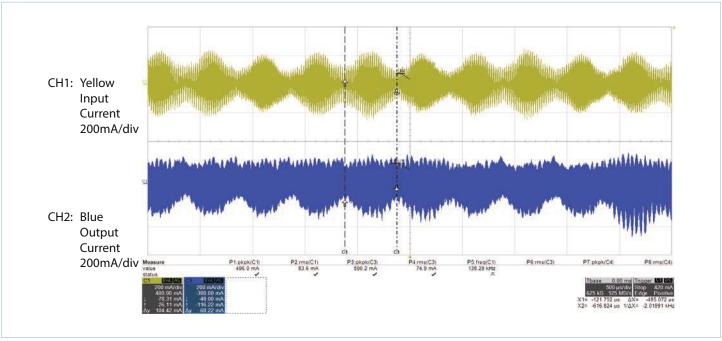

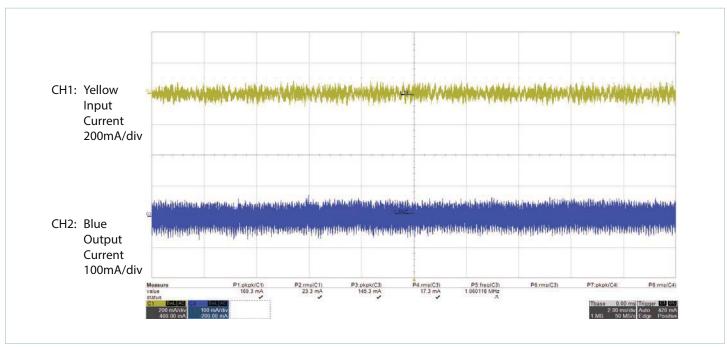

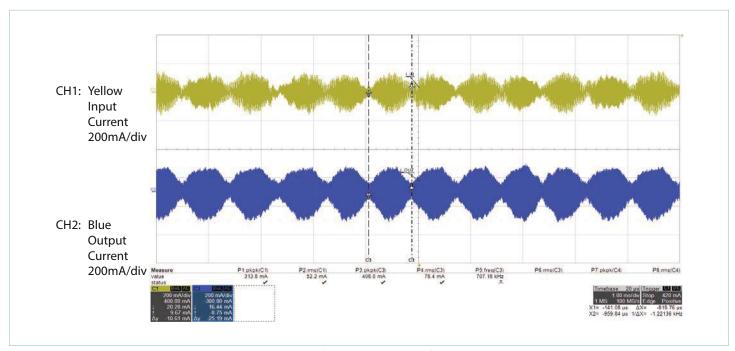

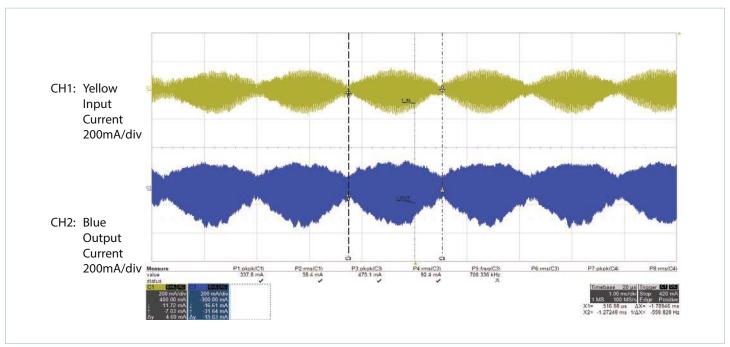

|              | remonstration of the Effect of Input and Output Filters<br>In the Beat Frequency Oscillations:                | 62        |

| <u>Ir</u>    | nput Filter                                                                                                   | 63        |

| <u>O</u>     | Output Filter                                                                                                 | 63        |

# **Table of Contents Cont.**

| 5. Achieving Improved Output Voltage or Current Regulation                                   | 68 |

|----------------------------------------------------------------------------------------------|----|

| Introduction                                                                                 | 68 |

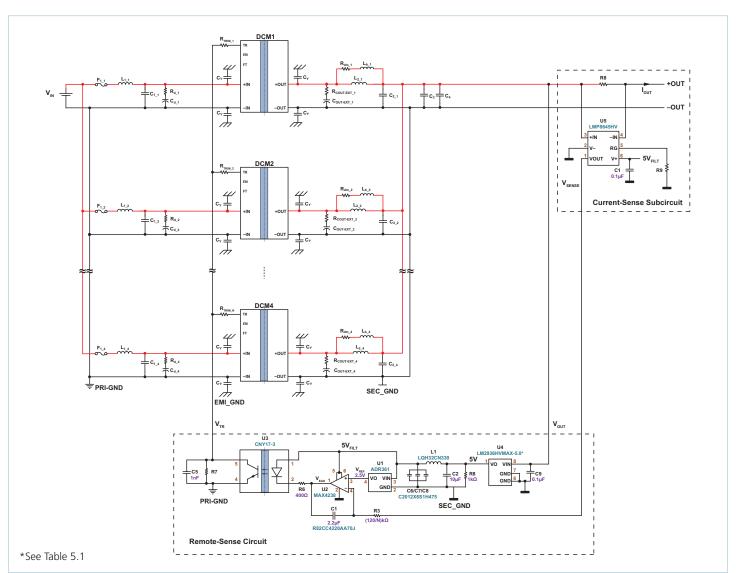

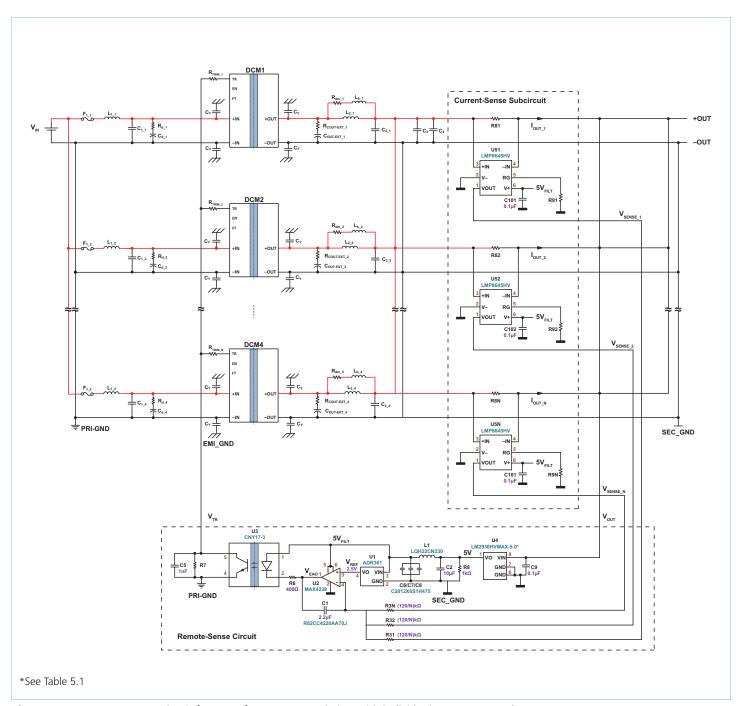

| Circuit Schematic                                                                            | 68 |

| Functional Description of Remote-Sense Circuit                                               | 69 |

| Component Selection                                                                          | 70 |

| Loop Compensation                                                                            | 71 |

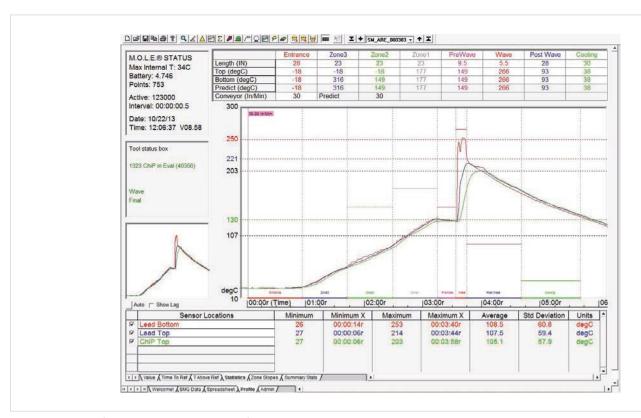

| Test Results (Steady State, Start Up, and Transient)                                         | 72 |

| Conclusion                                                                                   | 74 |

| Appendix I. Choosing R6 to Account for CTR Variance in the CNY17-3 Over Temperature and Time | 75 |

| Appendix II. Current Regulation                                                              | 76 |

| 6. Input / Output Series Operation – Not Recommended                                         | 78 |

| DCM Input Terminals in Series Configuration                                                  | 78 |

| DCM Output Terminals in Series Configuration                                                 | 78 |

| Unregulated Topologies                                                                       | 78 |

| Regulated Topologies                                                                         | 78 |

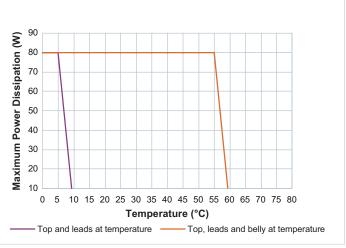

| 7. Thermal Management                                                                        | 79 |

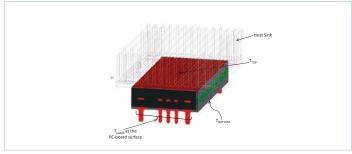

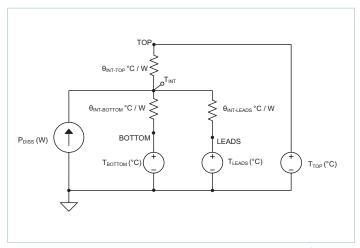

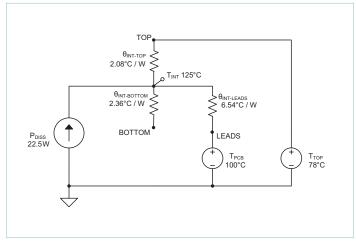

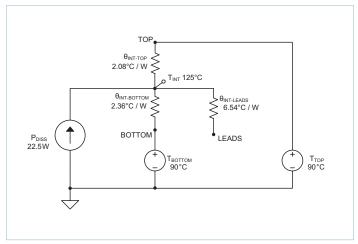

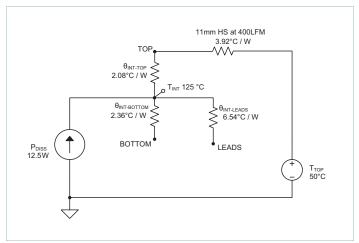

| Thermal Management                                                                           | 79 |

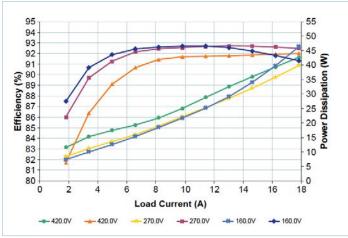

| Efficiency and Power Dissipation                                                             | 79 |

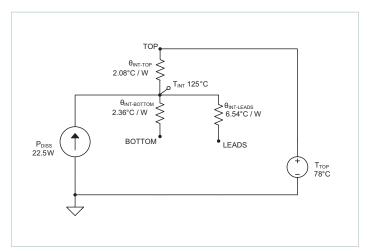

| Thermal Circuit Models                                                                       | 79 |

| Maximum Internal Temperature                                                                 | 79 |

| Use of Circuit Models                                                                        | 80 |

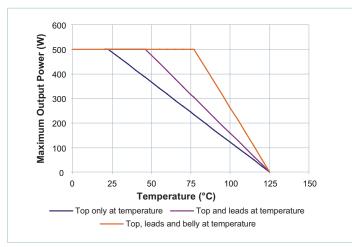

| Thermal Specified Operating Area                                                             | 82 |

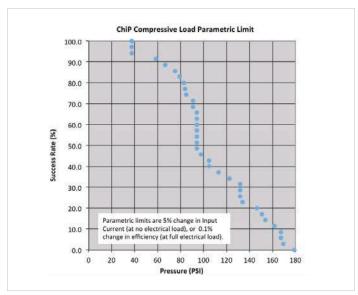

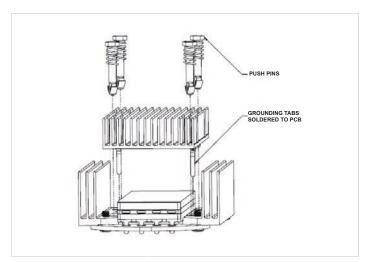

| Mechanical Compressive Force of Heat Sinks                                                   | 82 |

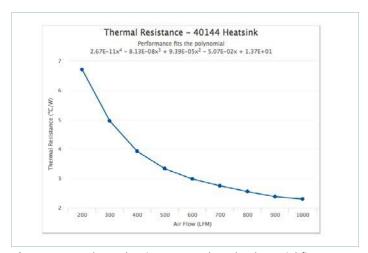

| Vicor Heat Sink                                                                              | 83 |

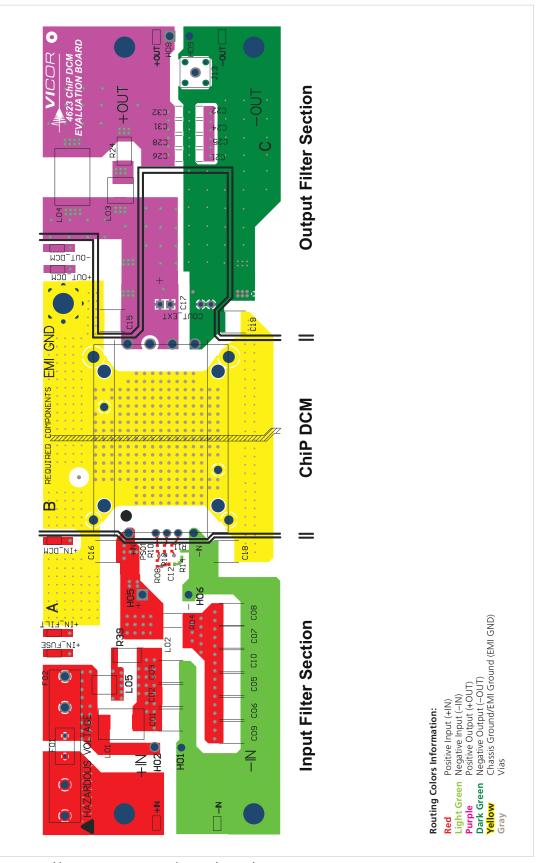

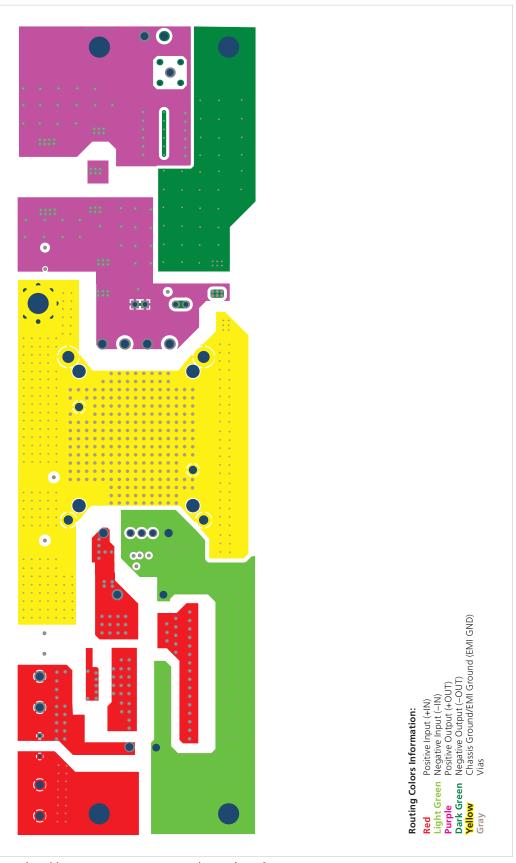

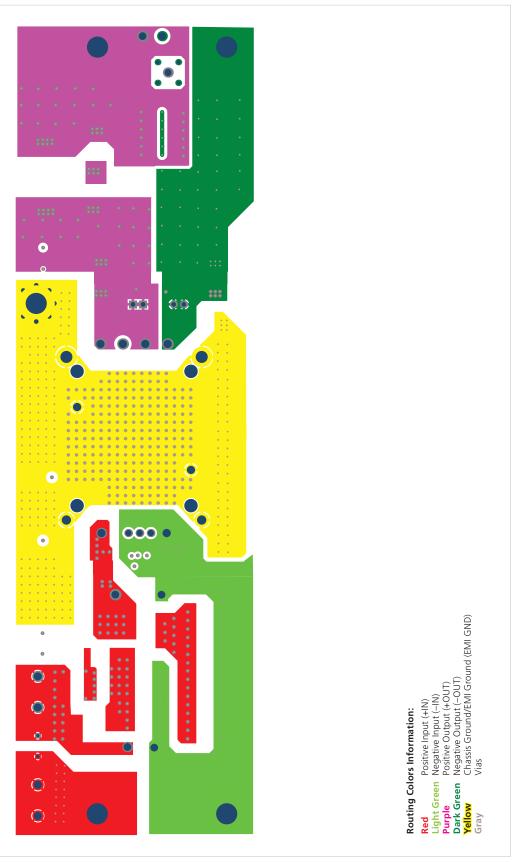

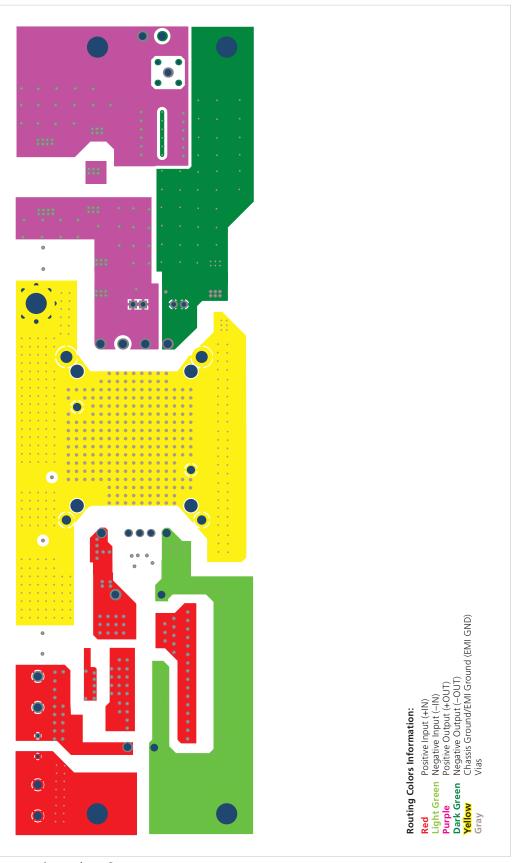

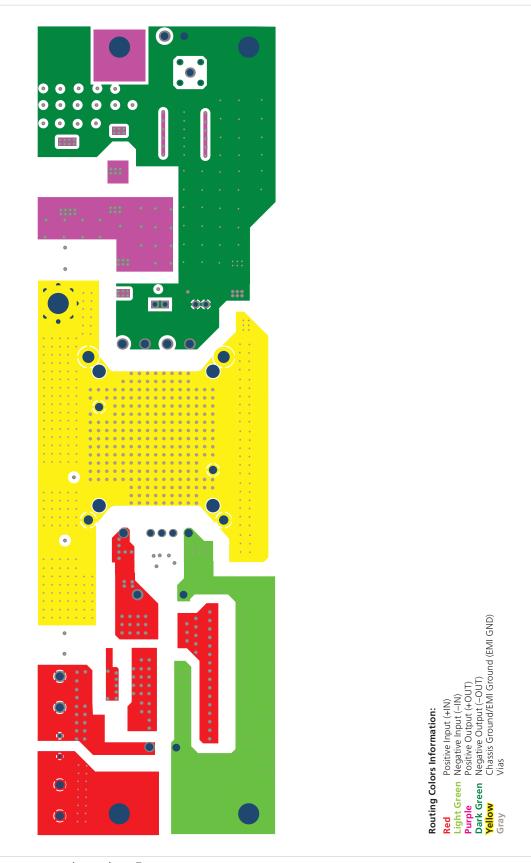

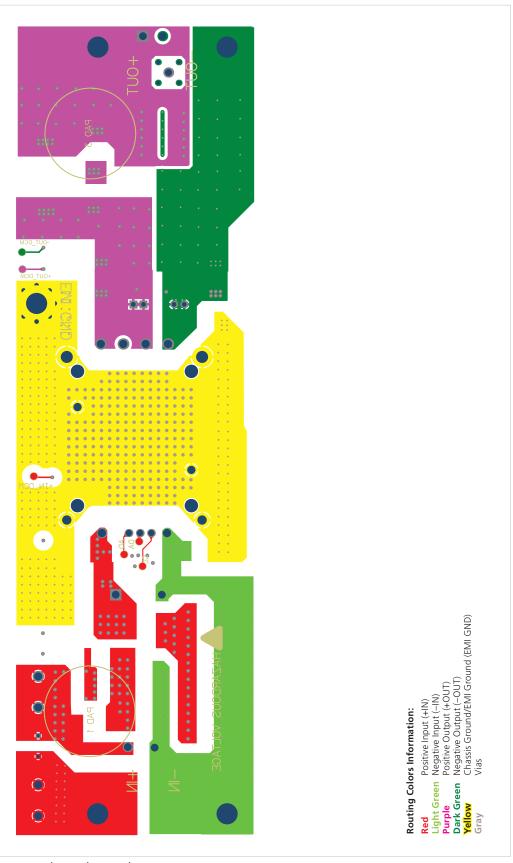

| 8. PC-Board Layout Considerations                                                            | 84 |

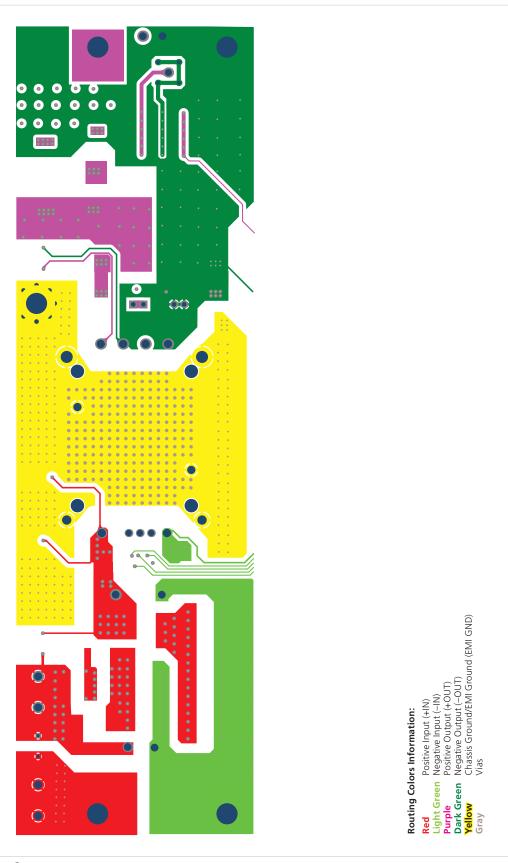

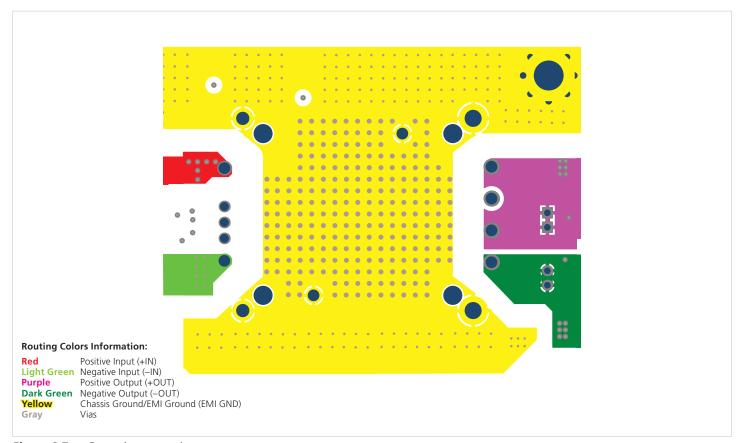

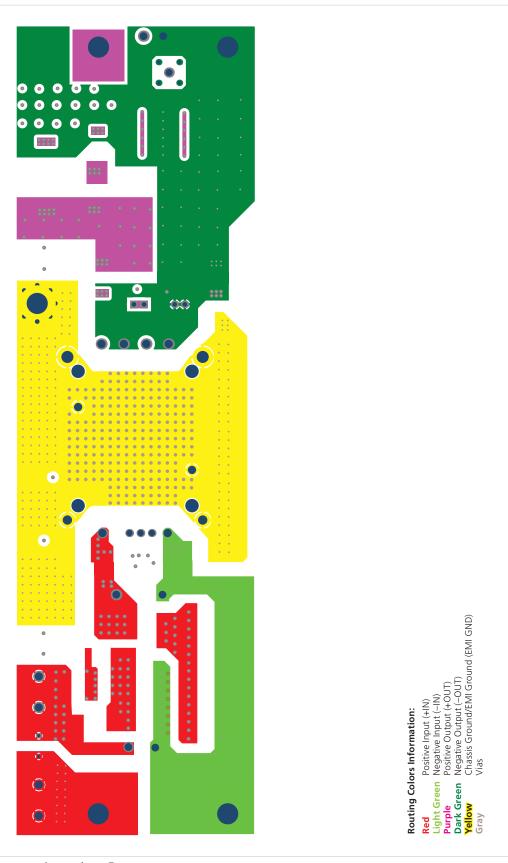

| PC-Board Layout Considerations and Component Placement for Improved EMI                      | 84 |

| 9. Soldering Considerations                                                                  | 96 |

| Disclaimer                                                                                   | 96 |

| <u>Handling</u>                                                                              | 96 |

| Soldering Process                                                                            | 97 |

| Removal                                                                                      | 97 |

| Revision History                                                                             | 98 |

As a part of the modular power system design methodology and to provide a great flexibility to the power system designers to achieve high-performance, cost-effective design of power distribution systems, Vicor introduced the family of DC-DC converter modules (DCM) in a ChiP package (Converter housed in a Package), shown in Figure 1.1. ChiP platform products use advanced magnetic structures that are integrated within high-density interconnect (HDI) substrates, together with power semiconductors, control ASICs and a microcontroller to provide superior electrical and thermal performance.

The DCMs can be used in various applications related to Commercial, Industrial and Military grades. A few examples of Commercial / Industrial-grade applications where DCMs best fit in are battery charging, LED lighting and medical devices. Also, applications such as data centers and telecommunications that require huge amounts of power can implement distributed power architecture using DCMs. This can improve the overall power system efficiency and lower the system and operational costs.

DCMs are well suited in Military grade applications such as ground based vehicular systems, targeting systems, flat panel displays, RF Jammers and airborne applications that require higher power levels and high reliability with size, weight and cost as an additional constraints.

One must be aware of the technical considerations when implementing a high-performance converter into the design of a power system. Therefore, this design guide is intended to provide power system designers with detailed insight to best use ChiP DCMs in a DC distribution power system.

#### Introduction to DC-DC converter Module (DCM)

The DCM encapsulates isolation, regulation, thermal management and fault monitoring in a single module. The DCM operates on a high-frequency, double-clamped zero voltage switching (DC-ZVS) topology. As a result of high-frequency operation, the size of the magnetics and energy storage elements are reduced. In turn, a revolutionary increase in density is achieved, with the power density up to 1244W/in<sup>3</sup>. As a result of double-clamped zero voltage switching (DC-ZVS) topology, high efficiency is achieved with efficiencies of up to 93% compared to other DC-DC converter solutions.

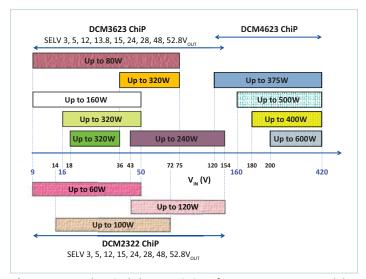

Figure 1.1 — Through-hole ChiP DCM

The DCM can operate from an unregulated, wide-range input voltage to provide an isolated and regulated output voltage with regulation of up to  $\pm 1\%$ . These are available in various regulated output voltages in the range of Safety Extra Low Voltage (SELV) from 3 – 53V. Specific details are described in the Figure 1.2. The DCM is capable of delivering high power levels of up to 600W in its standalone operation. In applications that call for more power than can be delivered by a single DCM, multiple DCMs can be used in parallel.

The DCMs are available in three package sizes with their respective specifications shown below:

- 2322 through-hole ChiP package

- 0.978 x 0.898 x 0.284in [24.84 x 22.8 x 7.21mm]

- Low input voltage range of 9 154V

- Maximum power up to 120W

- Input to output isolation of 3,000V<sub>DC</sub> (2,121V<sub>RMS</sub>)

- 3623 through-hole ChiP package

- 1.524 x 0.898 x 0.284in [38.72 x 22.8 x 7.21mm]

- Low input voltage range of 9 154V

- Maximum power up to 320W

- Input to output isolation of  $2,250V_{DC}$  (1,800 $V_{RMS}$ )

- Input to output isolation of 3,000V<sub>DC</sub> (2,121V<sub>RMS</sub>)

Note: Applicable only for 43 154V input voltage range products.

- 4623 through-hole ChiP package

- 1.886 x 0.898 x 0.284in [47.91 x 22.8 x 7.21mm]

- High input voltage range of 120 420V

- Maximum power up to 600W

- Input to output isolation of 4,242V<sub>DC</sub> (3,000V<sub>RMS</sub>)

**Figure 1.2** — Electrical characteristics of DC-DC converter module (DCM), MIL-COTS range is shown in blue

Apart from the previous electrical characteristics, other important features of the DCMs are:

- Droop share characteristics, which allows DCMs to be used in parallel operation for increasing power outputs without any requirement of external-control circuitry.

- Output voltage trimming typical trim range is -40% to +10% of the nominal output voltage.

- Fully operational current limit

- Enable / Disable control

- Various fault protections, it includes:

- Input undervoltage lockout (V<sub>IN UVI O</sub>)

- Input overvoltage lockout (V<sub>IN OVLO</sub>)

- Overtemperature

- Output overvoltage

- Overcurrent

- Short circuit

#### **Useful Links**

- DCM Family Page

- See individual product pages for accessories:

- Heat sinks

- U-shaped heat spreaders

- Environmental Qualification Test Reports

- Test data of the specific model with a specific serial number can be obtained from entering the model and serial number in the "Final Test Data" section of the Vicor Quality page.

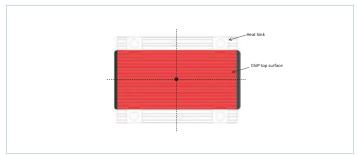

DCMs use a thermally-adept ChiP packaging technology which provides flexible thermal management. The ChiP's top and bottom sides are molded with an optimized thermal compound material that has low thermal impedance. This allows the internally-generated heat to evenly distribute across the surfaces of the ChiP and also enhances thermal pathways to the smooth, flat ChiP exterior. The majority of the heat can be removed using single- or dual-sided cooling using heat sinks or coldplates with some heat transfer through the leads of the package.

To help power system designers to fully leverage the electrical and thermal performance characteristics of the ChiP DCMs, Vicor offers following online design tools:

- PowerBench™ Whiteboard\*

- Product Simulators™

- DCM™ Trim Calculator

- \* Available on Internet Explorer and Chrome browsers only.

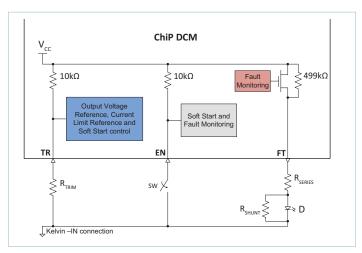

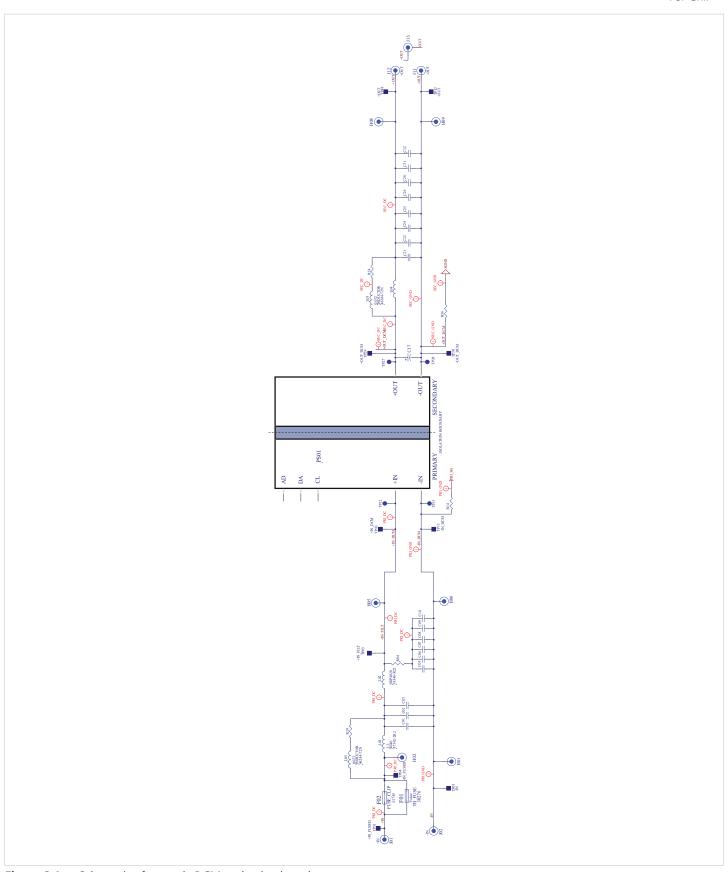

11. Control Pin Circuitry

sw<sup>y</sup>

Z<sub>OUT-FILTER</sub>

$R_{TRIM_1} >$

11B.

ise Filte

R<sub>SE 1</sub>

6. Slew Rate

Z<sub>TOTAL-SOURCE</sub>

$Z_{IN-DCM}$

D₁❖

TR

EN

FT

+IN

DCM™ Design Guide

#### 1. Source and Source Impedance

A. Consider source impedance L<sub>IN</sub>, R<sub>IN</sub> in total source impedance calculations, refer to the General Notes A.

#### 2. Input Line Impedance

A. Take input line impedance L<sub>D</sub>. R<sub>D</sub> into consideration while calculating the total source impedance. Follow guidelines per General Notes A.

#### 3. Decoupling Capacitor

- A. Select an optimum value of decoupling capacitor to compensate for source impedance and input line impedance (Z<sub>SOURCE</sub> point gives Thevenin's equivalent impedance looking back into the source and line).

- $\textbf{B.}\ \mathsf{R}_{\mathsf{ESR}\ \mathsf{DECOUPLE}}$  must be properly selected to provide optimum damping. The requirements of R<sub>ESR DECOUPLE</sub> can be satisfied by electing an Aluminum Electrolytic capacitor with an ESR value close to the desired value, this eliminates the need for an external damping resistor.

#### 4. Safety

- A. In case of failure of the DCM such as input short circuit, a fuse must be used to mitigate the risk of fire and board damage.

- B. Select recommended fuse from the Safety Approvals section of the DCM product family page.

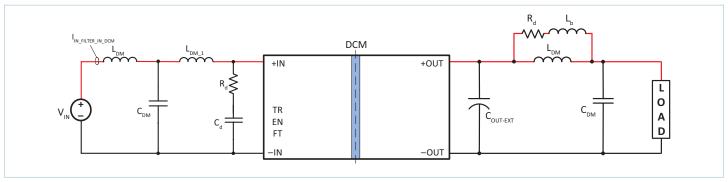

# Source ← 4. Safety F1 $L_D$ $R_D$ 2. Input Line 1. Source and **Impedance** Source Impedance

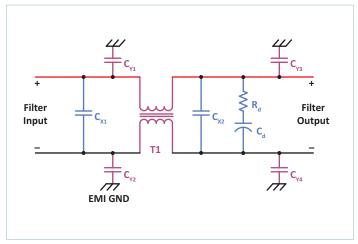

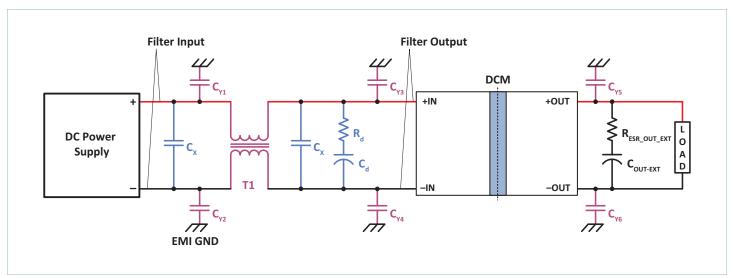

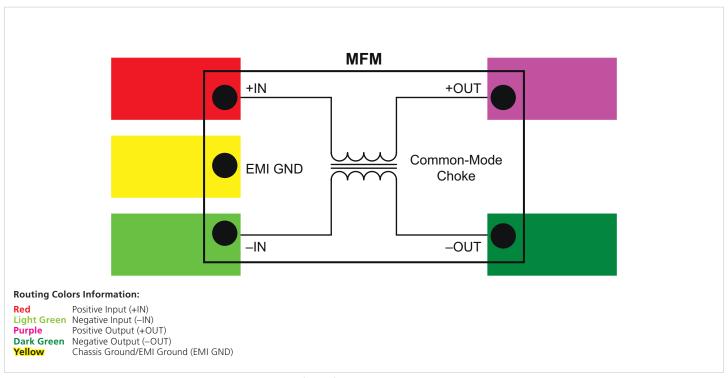

#### 7. Common-Mode Filter Network

- A. Switching converters are a source of common-mode noise; to attenuate common-mode noise Y-capacitors (C<sub>Y3 6</sub>) must be placed from +IN, -IN, +OUT, -OUT to earth/chassis ground.

- B. Y-capacitors must be placed as close as possible to the input and output pins of the module.

- C. Y-capacitor selection must meet application safety standards. Y2 sub-classification Y-capacitors are recommended with a typical capacitance value of 4700pF, with an appropriate peak voltage rating.

- D. Optional EMI Filter: To meet EMI requirements or for better common-mode noise attenuation, use a common-mode choke T1 along with the Y-capacitors ( $C_{Y1\ 4}$ ) on input of the DCM. Similar common-mode filtering network can be used on the output of the DCM to meet EMI requirements on the output side. See Common-Mode Input Filter Design considerations, page 36.

**Optional EMI Filter**

7D. Optional EMI Filter

L1

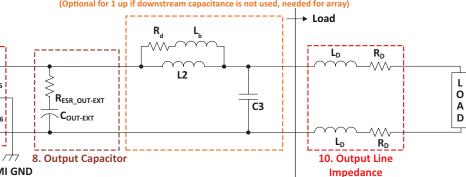

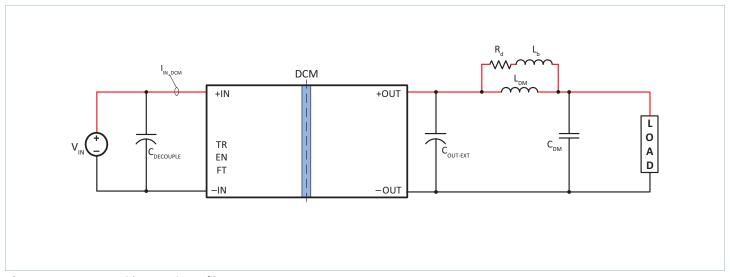

#### 9. Differential-Mode Output Filter (Optional)

- A. To attenuate differential-mode noise generated by switching converter, use a differential-mode filter network.

- B. Select the cutoff frequency of the output filter at least ten times lower than the switching frequency.

- **C.** Output filter must be well damped to avoid ringing in the output voltage.

- **D.** For high-frequency noise attenuation, use multiple low-ESR valued capacitors, such as ceramic capacitors, at C3.

#### 10. Output Line Impedance

DCM

A. Load regulation degrades due to excessive output line impedance. For better regulation at the load, keep the output line impedance as low as possible or consult app note AN:035 "Achieving High Accuracy Voltage (or Current) Regulation with the DCM up to ±1% regulation.

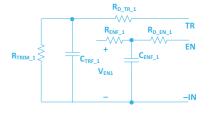

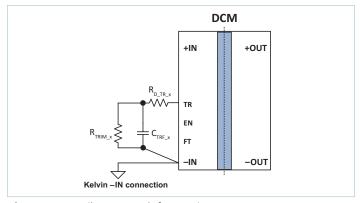

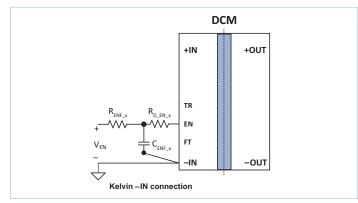

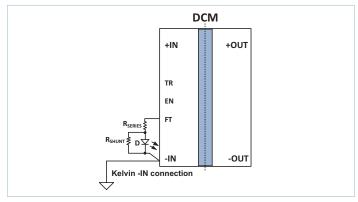

#### 11. Control Pin Circuitry

- A. Circuit on control pins, TR, EN, FT, must be referenced directly to –IN at the module input pin using a Kelvin connection.

- B. Optional Noise Filter: For protection from external noise the TR and EN pins may need an RCR filter network. R<sub>D TR 1</sub>, R<sub>D EN 1</sub> are provided for attenuating noise caused by the external lead inductance.

- C. Please refer to the DCM Trim Calculator to find the R<sub>TRIM 1</sub> value.

- **D.** Minimum loading of  $R_{SH-1} = 50k\Omega$  on FT pin is required for fault status indication. FT pin can provide a maximum current of 4mA, select a series resistor R<sub>SE 1</sub> to limit the current.

- **E.** If control / monitor functions are not required, signal pins can be left unconnected.

#### **Optional Noise Filter**

# 9. Differential-Mode Output Filter

(Optional for 1 up if downstream capacitance is not used, needed for array)

#### 5. Differential Mode Input Filter

- **A.** Switching converters are a source of the differential-mode noise; use a differential-mode filter network to attenuate differential-mode noise.

- **B.** Select the cutoff frequency of the input filter much lower than the DCM crossover frequency (20kHz).

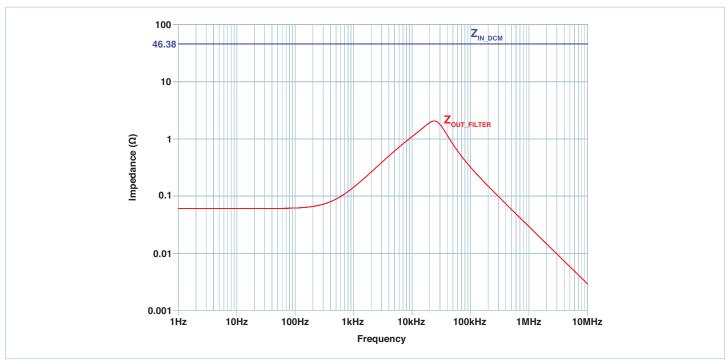

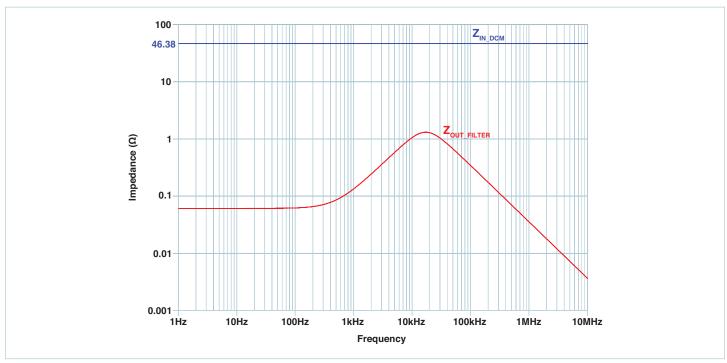

- **C.** Input filter must be well damped to avoid ringing of the input voltage. The impedance of the input filter looking back into the input filtering network from Z<sub>OUT\_FILTER</sub> must be at least ten times lower than the input impedance of the DCM (Z<sub>IN DCM</sub>). Please refer to the <u>filter design tool</u> to analyze the filter response.

#### 6. Slew Rate

A. Input voltage slew rate at the DCM input leads (+IN, -IN) must be less than 1V/µs.

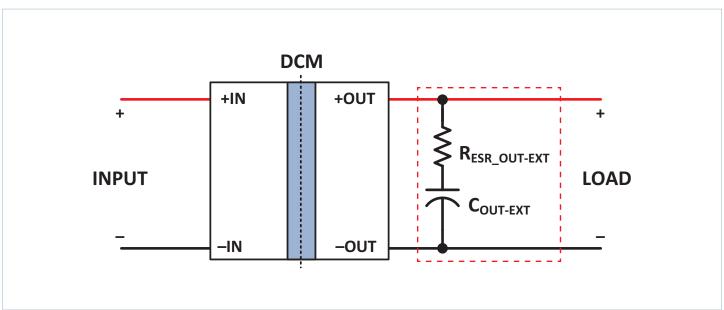

#### 8. Output Capacitor

RESR\_DECOUPLE

CDECOUPLE

3. Decoupling

Capacitor

**A.** For control-loop stability, the output capacitor must be within the Min / Max range of  $C_{\text{OUT\_EXT}}$  data sheet specifications, with a minimum  $R_{ESR\_OUT\_EXT}$  of  $10m\Omega$ .

$\bullet$  The requirement of  $R_{\text{ESR\_OUT\_EXT}}$  can be satisfied by selecting an aluminum electrolytic capacitor with an ESR of at least 10mΩ.

C1

5. Differential-Mode

**Input Filter**

- $\textbf{B.}\ \textbf{C}_{\text{OUT}\ \text{EXT}}$  must be placed physically near the output pins of the module.

- **C.** While choosing the output capacitor, operating / environmental temperature must be taken into consideration.

# **GENERAL NOTES:**

# A. Source Impedance and Its Effect on Stability

+OUT

-OUT

• Interaction between the total source impedance and input impedance of the DCM will cause stability issues. To avoid interactions, total impedance looking back into the source (Z<sub>TOTAL SOURCE</sub>) must be at least ten times lower than the input impedance of the DCM (Z<sub>IN DCM</sub>) over a frequency range of 0Hz to maximum control loop bandwidth:

$C_{Y6}$

EMI GND

$Z_{TOTAL\_SOURCE} \le (Z_{IN\_DCM} / 10)$  for all F[0 : 20kHz].

#### **B. Environmental Conditions**

7. Common-Mode 🖈

**Filter Network**

- Converters must be protected from environmental conditions such as moisture, dust, explosive or hazardous atmosphere. The DCM must be enclosed for safety during potentially higher operating temperature and voltage.

- Excessive heat, cold and thermal shock can cause damage of the ChiP.

- DCM should not be exposed to condensation.

#### C. Soldering the ChiP

- Follow the app note AN:031 "Through-Hole ChiP package soldering guidelines."

- Clean the PC board after the soldering process of the ChiP to remove the flux residues.

# D. Thermal Management of the ChiP

- Heat can be removed from the ChiP top and bottom surfaces, as well as through the leads.

- For more information, refer to app note AN:039 "Thermal Management for VIA™ and ChiP Modules."

#### E. Mechanical Compressive Force of Heat Sinks

- Excessive z-axis compressive force on the ChiP will cause a shift in electrical parameters and mechanical deformation of the leads.

- Maximum compressive force on the ChiP must be kept below 20psi. For more information, consult app note AN:036 "Recommendations for Maximum Compressive Force of Heat Sinks."

#### F. Product Simulator

• Use the **Product Simulator** for conducting thermal, start-up, steady-state, V<sub>IN</sub>-step and load-step simulations.

Note: Click any numbered heading on this page to jump to the related section of this Design Guide for more information.

# **Safety Considerations**

#### Fusing

To provide flexibility in designing a power system, the DCM converter is not internally fused. To meet safety standards, specific fuse recommendations are provided in the agency certifications. Fusing provides protection in case of a system or component failure such as an input short circuit and it will help mitigate the risk or spread of fire and board damage.

Safety approvals should always be consulted for the latest fusing requirements. Please refer to the <u>Safety Approvals</u> section of the DCM product family page.

A fuse must also be used for applications that do not require agency certifications. When selecting a fuse for these applications, the following characteristics should be taken into consideration:

- Voltage rating

- The device voltage rating should be greater than the maximum possible input voltage

- Current rating

- The device current rating should be greater than the DCM converter's maximum input current

- Interrupting rating, very important for low-impedance sources

- Temperature de-rating

- Melting integral (I²t)

|                              | Acceptable Fus            | se Types and Curren     | t Rating for the DCM ChiP Family | of Converters                           |

|------------------------------|---------------------------|-------------------------|----------------------------------|-----------------------------------------|

| put Voltage Range<br>(Volts) | Output Voltage<br>(Volts) | Output Power<br>(Watts) | ChiP Model Number                | Recommended Fuse                        |

|                              |                           |                         | DCM2322                          |                                         |

|                              | 12                        | 60                      | DCM2322x50T1360y6z               | Littelfuse 487 10A<br>EATON ABC 10A     |

|                              | 15                        | 60                      | DCM2322x50T1760y6z               |                                         |

| 30 (9 – 50)                  | 24                        | 60                      | DCM2322x50T2660y6z               |                                         |

|                              | 28                        | 60                      | DCM2322x50T3160y6z               | 2/11/01/11/15/01/11                     |

|                              | 48                        | 60                      | DCM2322x50T5360y6z               |                                         |

|                              | 3.3                       | 35                      | DCM2322x72S0435y6z               | Littelfuse 487 8A                       |

|                              | 5                         | 50                      | DCM2322x72S0650y6z               | EATON ABC 8A                            |

|                              | 12                        | 100                     | DCM2322x72S13A0y6z               |                                         |

| 43 (14 – 72)                 | 15                        | 100                     | DCM2322x72S17A0y6z               | Littelfuse 487 12.5A<br>EATON ABC 12A   |

|                              | 24                        | 100                     | DCM2322x72S26A0y6z               |                                         |

|                              | 28                        | 100                     | DCM2322x72S31A0y6z               |                                         |

|                              | 48                        | 100                     | DCM2322x72S53A0y6z               |                                         |

|                              | 3.3                       | 40                      | DCM2322xA5N0440y6z               |                                         |

|                              | 5                         | 60                      | DCM2322xA5N0660y6z               |                                         |

|                              | 12                        | 120                     | DCM2322xA5N13A2y6z               |                                         |

| 100 (43 – 154)               | 15                        | 120                     | DCM2322xA5N17A2y6z               | EATON BK/PCE-5-R                        |

|                              | 24                        | 120                     | DCM2322xA5N26A2y6z               |                                         |

|                              | 28                        | 120                     | DCM2322xA5N31A2y6z               |                                         |

|                              | 48                        | 120                     | DCM2322xA5N53A2y6z               |                                         |

|                              |                           |                         | DCM3623                          |                                         |

|                              | 3.3                       | 80                      | DCM3623x50T0480yzz               | Bussmann ABC-15-R                       |

|                              | 5                         | 80                      | DCM3623x50T0680yzz               | Littelfuse 456 20A                      |

| 30 (9 – 50)                  | 12                        | 160                     | DCM3623x50T13A6yzz               |                                         |

|                              | 15                        | 160                     | DCM3623x50T17A6yzz               | Bussmann ABC-30-R<br>Littelfuse 456 30A |

|                              | 24                        | 160                     | DCM3623x50T26A6yzz               |                                         |

|                              | 28                        | 160                     | DCM3623x50T31A6yzz               |                                         |

|                              | 48                        | 160                     | DCM3623x50T53A6yzz               |                                         |

|                              |                           |                         |                                  |                                         |

|                              | Acceptable Fuse T         | ypes and Current Ra  | ting for the DCM ChiP Family of C | Converters (Cont.)                                                       |

|------------------------------|---------------------------|----------------------|-----------------------------------|--------------------------------------------------------------------------|

| put Voltage Range<br>(Volts) | Output Voltage<br>(Volts) | Output Power (Watts) | ChiP Model Number                 | Recommended Fuse                                                         |

|                              |                           | DC                   | M3623 (Cont.)                     |                                                                          |

|                              | 5                         | 180                  | DCM3623x36G06A8yzz                | Bussmann ABC-15-R                                                        |

|                              | 12                        | 320                  | DCM3623x36G13C2yzz                | Bussmann ABC-30-R                                                        |

| 24 (18 – 36)                 | 15                        | 320                  | DCM3623x36G17C2yzz                |                                                                          |

|                              | 24                        | 320                  | DCM3623x36G26C2yzz                |                                                                          |

|                              | 28                        | 320                  | DCM3623x36G31C2yzz                |                                                                          |

|                              | 36                        | 320                  | DCM3623x36G40C2yzz                |                                                                          |

|                              | 48                        | 320                  | DCM3623x36G53C2yzz                |                                                                          |

|                              | 12                        | 80                   | DCM3623x75X1380yzz                |                                                                          |

|                              | 15                        | 80                   | DCM3623x75X1780yzz                |                                                                          |

| 42 (9 – 75)                  | 24                        | 80                   | DCM3623x75X2680yzz                | Littelfuse 487 15A<br>Bussmann ABC-15-R                                  |

|                              | 28                        | 80                   | DCM3623x75X3180yzz                |                                                                          |

|                              | 48                        | 80                   | DCM3623x75X5380yzz                |                                                                          |

|                              | 3.3                       | 120                  | DCM3623x50M04A2yzz                | Bussmann ABC-12-R                                                        |

| 28 (16 – 50)                 | 5                         | 180                  | DCM3623x50M06A8yzz                | Bussmann ABC-18-R                                                        |

|                              | 12                        | 320                  | DCM3623x50M13C2yzz                | Bussmann ABC-30-R<br>Littelfuse 456 30A                                  |

|                              | 15                        | 320                  | DCM3623x50M17C2yzz                |                                                                          |

|                              | 24                        | 320                  | DCM3623x50M26C2yzz                |                                                                          |

|                              | 28                        | 320                  | DCM3623x50M31C2yzz                |                                                                          |

|                              | 48                        | 320                  | DCM3623x50M53C2yzz                |                                                                          |

|                              | 5                         | 160                  | DCM3623x75H06A6yzz                | Bussmann ABC-7-R                                                         |

|                              | 12                        | 320                  | DCM3623x75H13C2yzz                |                                                                          |

|                              | 15                        | 320                  | DCM3623x75H17C2yzz                |                                                                          |

| 48 (36 – 75)                 | 24                        | 320                  | DCM3623x75H26C2yzz                | Bussmann ABC-15-R                                                        |

|                              | 28                        | 320                  | DCM3623x75H31C2yzz                | DUSSINATIN ABC-13-K                                                      |

|                              | 36                        | 320                  | DCM3623x75H40C2yzz                |                                                                          |

|                              | 48                        | 320                  | DCM3623x75H53C2yzz                |                                                                          |

| 100 (43 – 154)               | 3.3                       | 80                   | DCM3623xA5N0480yzz                | Littelfuse 487 8A<br>Cooper Bussman PC-Tron PCB-3-R,<br>PCB-4-R, PCD-5-R |

|                              | 5                         | 120                  | DCM3623xA5N06A2yzz                | Littelfuse 487 8A<br>Bussman PC-Tron PCD-5-R                             |

|                              | 12                        | 240                  | DCM3623xA5N13B4yzz                |                                                                          |

|                              | 15                        | 240                  | DCM3623xA5N17B4yzz                |                                                                          |

|                              | 24                        | 240                  | DCM3623xA5N26B4yzz                | Littelfuse 487 8A<br>Bussmann ABC-10-R                                   |

|                              | 28                        | 240                  | DCM3623xA5N31B4yzz                |                                                                          |

|                              | 48                        | 240                  | DCM3623xA5N53B4yzz                |                                                                          |

| Acceptable Fuse Types and Current Rating for the DCM ChiP Family of Converters (Cont.) |                           |                         |                    |                          |  |  |

|----------------------------------------------------------------------------------------|---------------------------|-------------------------|--------------------|--------------------------|--|--|

| Input Voltage Range<br>(Volts)                                                         | Output Voltage<br>(Volts) | Output Power<br>(Watts) | ChiP Model Number  | Recommended Fuse         |  |  |

|                                                                                        | DCM4623                   |                         |                    |                          |  |  |

|                                                                                        | 3.3                       | 110                     | DCM4623xD2N04A1yzz | Bussmann PC-Tron PCB-3-R |  |  |

|                                                                                        | 5                         | 190                     | DCM4623xD2N06A9yzz | Bussmann PC-Iron PCB-3-R |  |  |

|                                                                                        | 12                        | 375                     | DCM4623xD2N13C8yzz |                          |  |  |

| 275 (120 – 420)                                                                        | 15                        | 375                     | DCM4623xD2N17C8yzz |                          |  |  |

|                                                                                        | 24                        | 375                     | DCM4623xD2N26C8yzz | Bussmann PC-Tron PCD-5-R |  |  |

|                                                                                        | 28                        | 375                     | DCM4623xD2N31C8yzz |                          |  |  |

|                                                                                        | 48                        | 375                     | DCM4623xD2N53C8yzz |                          |  |  |

|                                                                                        | 3.3                       | 150                     | DCM4623xD2K04A5yzz | Bussmann PC-Tron PCB-3-R |  |  |

|                                                                                        | 5                         | 250                     | DCM4623xD2K06B5yzz | Bussmann PC-Tron PCB-3-R |  |  |

|                                                                                        | 12                        | 500                     | DCM4623xD2K13E0yzz |                          |  |  |

| 270 (160 – 420)                                                                        | 15                        | 500                     | DCM4623xD2K17E0yzz | Bussmann PC-Tron PCD-5-R |  |  |

|                                                                                        | 24                        | 500                     | DCM4623xD2K26E0yzz |                          |  |  |

|                                                                                        | 28                        | 500                     | DCM4623xD2K31E0yzz |                          |  |  |

|                                                                                        | 48                        | 500                     | DCM4623xD2K53E0yzz |                          |  |  |

| 300 (180 – 420)                                                                        | 12                        | 400                     | DCM4623xD2J13D0yzz | Bussmann PC-Tron PCB-5-R |  |  |

| 290 (160 – 420)                                                                        | 13.8                      | 600                     | DCM4623xC8G16F0yzz | Bussmann PC-Tron PCD-5-R |  |  |

|                                                                                        | 24                        | 600                     | DCM4623xD2H26F0yzz | Bussmann PC-Tron PCD-5-R |  |  |

| 300 (200 – 420)                                                                        | 13.8                      | 500                     | DCM4623xD2H15E0yzz |                          |  |  |

| 300 (200 – 420)                                                                        | 28                        | 500                     | DCM4623xD2H31E0yzz | Bussmann PC-Tron PCD-5-R |  |  |

|                                                                                        | 48                        | 500                     | DCM4623xD2H53E0yzz |                          |  |  |

#### **DCM Output Capacitor**

To ensure proper operation of the DCM, the capacitance of the load must be within the limits that are defined in the data sheet by  $C_{\text{OUT-EXT}}$  for normal operation. The maximum limit is required to avoid excessive start-up time, which could trigger output undervoltage fault protection. The minimum limit for  $C_{\text{OUT-EXT}}$ , as well as the minimum ESR of the external capacitor,  $R_{\text{COUT-EXT}}$ , are needed to ensure control loop stability.

For applications where the DCM sees very light loading, certain DCM models have increased minimum required external output capacitor values. The higher values depend on the load transients and the trim transients that the application imposes on the DCM. During Light-Load Boosting, a sudden change in the load – for instance, a step increase from a light load condition – may not be tracked by the control loop, as explained above. If there is not enough capacitance on the output, this could cause the output voltage to drop below the undervoltage fault protection threshold  $V_{\rm OUT-UVP}$ , causing shut down. (See Output Undervoltage Fault Protection (UVP) in the Fault Handling sub-section of the Standalone Operation section on page 43.)

To prevent this from happening, the minimum allowed output capacitance value must be increased so that it falls in the range given by  $C_{OUT-EXT-TRANS}$ . This effect is amplified for applications which dynamically trim the DCM output at the same time these load transients are occurring. In this case, the minimum allowed output capacitance must be further increased, per the limits of  $C_{OUT-EXT-TRANS-TRIM}$ , to prevent the load transient and dynamic trim event from triggering fault protection.

# **Location of Output Capacitor**

Any additional impedance between the DCM output pins and output capacitor may lead to control loop stability issue. Therefore, the output capacitor must be placed physically near the output pins of the DCM module as shown in Figure 2.1.

**NOTE:** While choosing the output capacitor, operating / environmental temperature must be taken into consideration.

Figure 2.1 — Location of external output capacitor

#### **Referencing of Input and Output Terminals**

The input and output leads of the DCM should be referenced to the EMI ground plane at some point to avoid stray voltages. For offline applications the input leads are often referenced to earth ground at the AC source ahead of the bridge rectifier. Either + or –Output terminal may be referenced to earth ground. "Floating" inputs or outputs should at a minimum have a high-resistance divider to bleed off stray charges to avoid damage to the insulation system.

# **Filtering Guidelines Introduction**

This section of the design guide is divided into three sub-sections, each sub-section provides guidelines on the following topics.

# Source Impedance and its Effects on Performance of the Switching Converters

The focus of this sub-section is to provide design guidelines and simulations on selecting an optimum value of decoupling capacitor and its equivalent series resistance (ESR) for reducing the source impedance.

# ■ Input Filter Design and Simulation

This sub-section focuses on the design and simulation of a typical differential-mode input filter network using the spice simulation tool and also provides actual measurements of the noise current of the DCM with and without input filters. In addition, Vicor also offers the Filter Design Tool, an online calculator that allows users to analyze the performance characteristics of various filtering network topologies with user defined filtering component values. Please refer to the following link:

http://app2.vicorpower.com/filterDesign/intiFilter.do

# ■ Common-Mode Input Filter Design

This sub-section provides information on common-mode noise sources, noise-mitigation techniques and focuses on the design of the common-mode noise filter.

Aforementioned sub-sections 1, 2 are general methodologies used in power system designs to reduce the effect of source impedance and to mitigate the differential mode noise generated by the switching converters. Sub-section 3 is a common method used to mitigate the common mode noise generated by the switching converters. Information presented on the common mode input filter design is confined to theoretical aspects of common mode noise filtering, if the system have to meet a particular EMI standards (such as MIL-STD, EN etc.), Vicor offers EMI filter solutions specifically designed to DCM product line; please contact Applications Engineering for more details.

# Source Impedance and its Effects on Performance of the Switching Converters

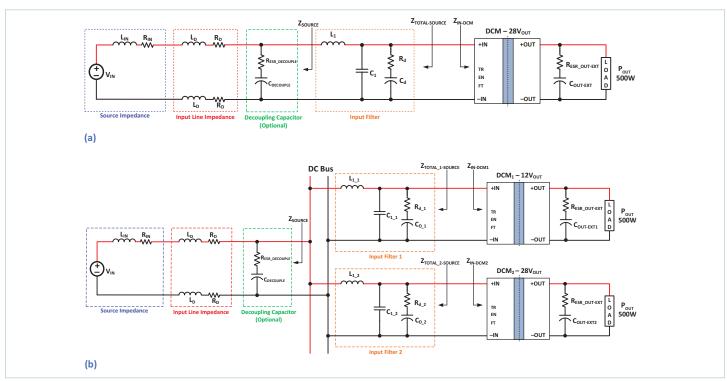

Typically switching power converters, including the DCM, are well designed to exhibit good stability margins and certain performance characteristics in their standalone operation. However, when a single or multiple converters are designed into a DC distribution system, illustrated in Figure 2.2, the interactions between the negative incremental input impedances of the converter(s) and the total output impedance of the source will alter the dynamic performance characteristics of the switching converters and also causes system-level instabilities. The interaction of the impedances is shown in Figure 2.6. These issues are a consequence of:

- Constant power loads (regulated converters) existing throughout the DC distribution system

- **b.** Interactions among the several converter feedback control loops tied at the DC bus

**Note:** The total output impedance of the source viewed from the  $Z_{\text{TOTAL-SOURCE}}$  point , shown in Figure 2.2, is Thevenin equivalent impedance of source, distribution line and input filter impedances.

System instability can be avoided by keeping the total output impedance of the source ( $Z_{\text{TOTAL-SOURCE}}$ ) at least ten times lower than the input impedance ( $Z_{\text{IN-DCM}}$ ) of the DCM over a frequency range of DC to the maximum control loop bandwidth:

$Z_{TOTAL\text{-}SOURCE} \le (Z_{IN\text{-}DCM}/10) \text{ for all } F[0:20kHz].$

This can be achieved by choosing the optimum value of the decoupling capacitor network along with proper design of the input filtering network.

Figure 2.2 — Typical DC-DC distribution system using DCMs: (a) single converter system, (b) multiple converter system

As a common practice, a high value of the decoupling capacitor network is placed on the DC bus, as shown in Figure 2.2. However, placing a large, bulk decoupling capacitor may not effectively reduce the effect of source impedance, but will adversely increase the required printed circuit board area. Therefore, the decoupling capacitor must be optimally selected based on the source impedance and distribution line impedance. In the cases where the source impedance and distribution line impedance are not significant enough to cause interaction with the input impedance of the switching converter, an adequately damped input filter may only enough to keep the Z<sub>TOTAL-SOURCE</sub> lower than the Z<sub>IN-DCM</sub>.

For quick reference only: Follow these steps to select an optimum value of decoupling capacitor and its ESR:

**Step 1:** Calculate the negative incremental input impedance  $(Z_{IN-DCM})$  of the DCM using Equation 2.1.

**Step 2:** Identify the source and line impedances. Represent the system in simpler way by separating the system into source and load subsystems.

**Step 3:** Plot the impedances vs. frequency using spice simulation tool. Identify the interaction.

**Step 4:** Select resonant frequency ( $f_{SOURCE}$ ) much lower than the DCM control loop bandwidth (20kHz). Calculate the decoupling capacitor using the Equation 2.2.

**Step 5:** Calculate the required ESR of decoupling capacitor using the Equation 2.3.

**Step 6:** Plot the impedance vs. frequency response in spice by modifying the Step 3 simulation model.

Verify there is no interaction between the impedances.

# Negative Incremental Input Impedance (Z<sub>IN-DCM</sub>)

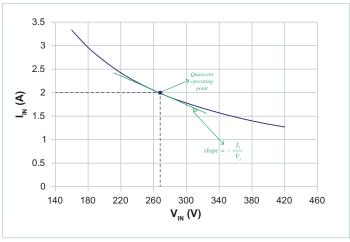

The DCM, as a feedback controlled switching converter, generates a regulated, isolated DC output voltage for a given range of input voltage and load current. Therefore, for a given load, the output power is constant irrespective of input voltage. This means that the input power is also constant such that as the input voltage is increased, the corresponding input current decreases and vice-versa, shown in Figure 2.3. Thus, the DCM behaves as a constant power load at its input terminals up to the control loop bandwidth; the DCM presents a negative incremental impedance ( $Z_{\text{IN-DCM}}$ ) at its input terminals and when interacting with the Thevenin equivalent source impedance ( $Z_{\text{TOTAL-SOURCE}}$ ), may result in system-level stability issues.

At any Quiescent operating point, the system can be considered linear and the slope of the resulting linear input current curve is negative, shown in Figure 2.3; thus, the Z<sub>IN-DCM</sub> is negative. Theoretically, the negative incremental impedance magnitude can be calculated using the Equation 2.1. For more detailed mathematical analysis on the input impedance and its effects on system stability and performance, please refer to the article below:

powerblog.vicorpower.com/wp-content/uploads/2009/10/tech\_tip\_input\_source\_impedance.pdf

Where

$$Z_{IN\text{-}DCM} = -\frac{V_I^2}{P_I} \quad or -\frac{\Delta V_I}{\Delta I_I} \text{ for all } F [0:20kHz] \qquad 2.1$$

$Z_{IN-DCM}$  = Negative incremental impedance of the DCM

$V_I =$  Input voltage to the DCM

$I_{I} = Input current of the DCM$

$P_I =$  Input power of the DCM

$\Delta V_I =$  Change in the input voltage of the DCM

$\Delta I_I$  = Change in the input current of the DCM

F = Control loop bandwidth of the DCM

As an example, DCM4623TD2K31E0T00 ( $160-420V_{IN}$ ,  $28V_{OUT}$ , 500W) with a constant output power of 500W is considered. The input power, accounting for operational power dissipation is calculated to be 533W. For an input voltage range of 160 to 420V, the worst case value of  $Z_{IN-DCM}$  is at the low line. The input current drawn by the DCM is 3.33A and the resulting negative incremental impedance is:

$$Z_{IN-DCM} = -\frac{160V}{3.33A} \text{ or } -\frac{(160V)^2}{533W} = -48\Omega$$

**Figure 2.3** —  $V_{IN}$  vs.  $I_{IN}$  characteristics at the DCM input terminals, with constant  $P_{OUT}$

Note that the  $Z_{\text{IN-DCM}}$  above the range of control loop bandwidth (F) of the DCM will be same as the open loop input impedance of the DCM. For the sake of simplicity,  $Z_{\text{IN-DCM}}$  is assumed to be constant over the entire frequency range of interest, as shown in Figure 2.6.

# **Stability Analysis**

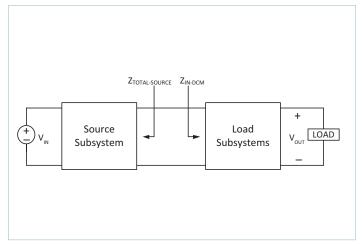

To conduct system stability analysis on a complex DC distribution system, shown in Figure 2.2, a simpler representation is first constructed by separating the system into source and load subsystems connected at an arbitrary interface as illustrated in Figure 2.4.

**Figure 2.4** — Block diagram representation of interacting source and load subsystems

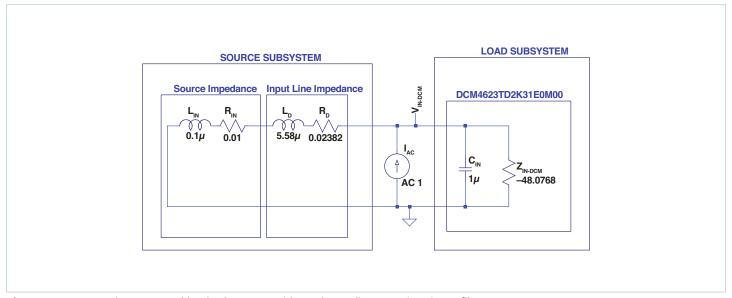

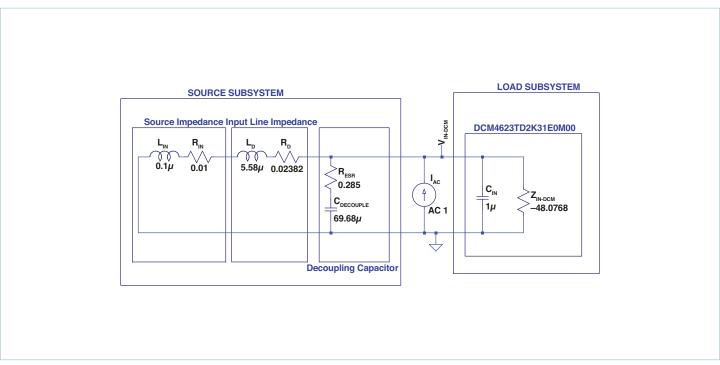

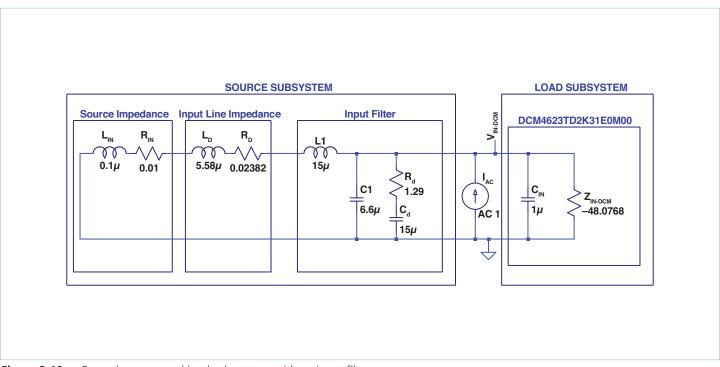

To demonstrate the interaction, an spice simulation model, shown in Figure 2.5, is designed and analyzed with a  $0.01\Omega$  output resistance  $(R_{\text{IN}}),\,0.1\mu\text{H}$  output inductance  $(L_{\text{IN}})$  power source and a 12-gauge, 15ft length distribution line. Using the commonly available online tools for wire impedance calculations, the parallel wire distribution line inductance  $(L_D)$  and line resistance  $(R_D)$  are calculated based on the assumption that the center-to-center distance between the parallel wires is 2cm.

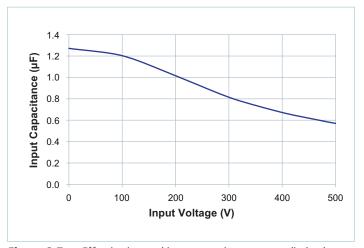

**NOTE:** The internal capacitance of the DCM ( $C_{\rm IN}$ ) is considered in these simulations (for the value of internal capacitance, please refer to the Figure "Effective internal input capacitance vs. applied voltage" in the DCM4623TD2K31E0T00 data sheet (copied in Figure 2.7).

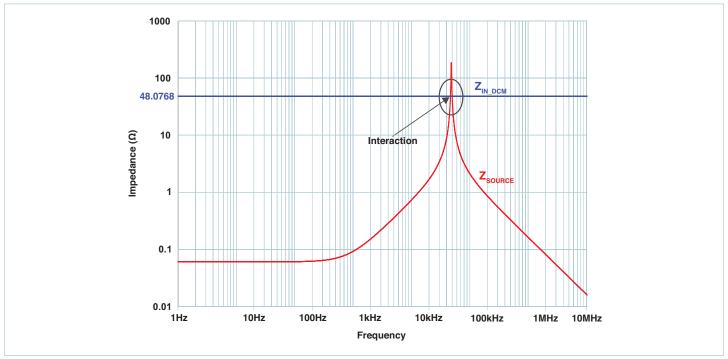

From the simulation results, shown in Figure 2.6, it can be observed that there is an interaction between  $Z_{SOURCE}$  and  $Z_{IN-DCM}$  at 65kHz. As mentioned above, to avoid interactions, the source and distribution line impedance must be at least ten times lower than the input impedance of the DCM over a frequency range of DC to the maximum control loop bandwidth (20kHz).

Figure 2.5 — Example source and load subsystems without decoupling capacitor, input filter

Figure 2.6 — Interaction between the output impedance of the source and the input impedance of the DCM

Figure 2.7 — Effective internal input capacitance vs. applied voltage

# **Optimum Value of Decoupling Capacitor**

The interactions can be avoided and the stability of the system can be ensured by placing a decoupling capacitor network after the source and input line impedances. This is effectively an LC filter network when viewed from  $Z_{\text{SOURCE}}$  point, refer to Figure 2.2. The source, line inductor and decoupling capacitor impedance asymptotes intersect at the LC filter resonant frequency ( $f_{\text{SOURCE}}$ ) and by placing the pole at the desired frequency, the optimum value of decoupling capacitor can be determined, which is given in the Equation 2.2:

$$f_{SOURCE} = \frac{1}{2\pi\sqrt{(L_{EO})\left(C_{DECOUPLE}\right)}} \qquad 2.2$$

Where:

$L_{FO} = L_D + L_{IN}$ , and

$L_{EQ}$  = Equivalent source inductance,

$L_D$  = Distribution line inductance,

$L_{IN}$  = Power source output inductance.

The required ESR of the decoupling capacitor can be determined using the characteristic impedance of the source LC filter network. The characteristic impedance is given in the Equation 2.3:

$$R_{O_{SOURCE}} = \sqrt{\frac{L_{EQ}}{C_{DECOUPLE}}}$$

2.3

For the above example, the peak output impedance of the source must be kept below the DCM control loop bandwidth. Thus, to find the optimum value of decoupling capacitor, fsource is chosen to be 8kHz. By substituting the values of  $L_{EQ}$  and fsource in Equation 2.2, the value of  $C_{DECOUPLE}$  is calculated as 69.68µF. By substituting the values of  $L_{EQ}$  and  $C_{DECOUPLE}$  in Equation 2.3, the ESR value is calculated as 0.285 $\Omega$ . The simulation of the system with an additional decoupling capacitor is shown in Figure 2.8.

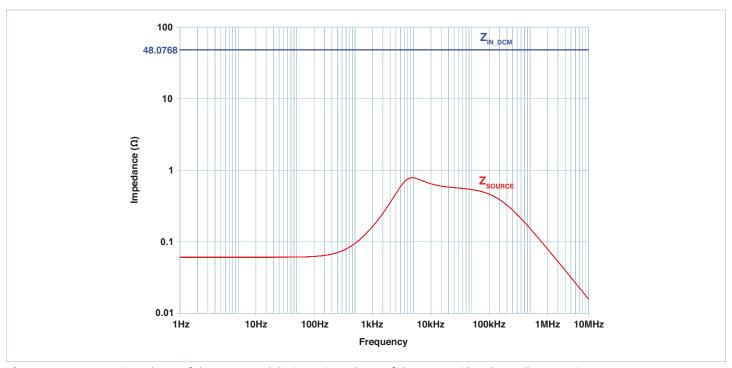

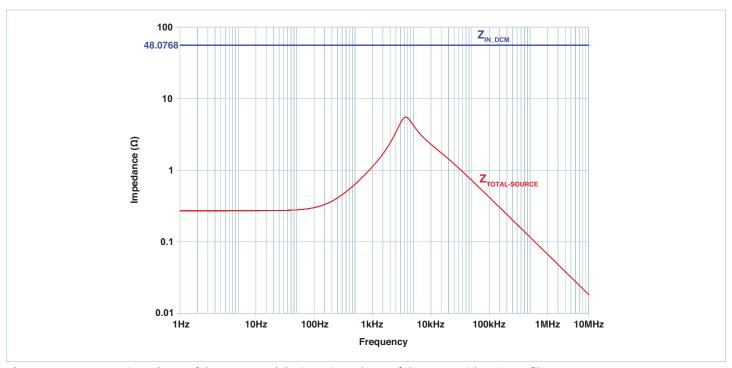

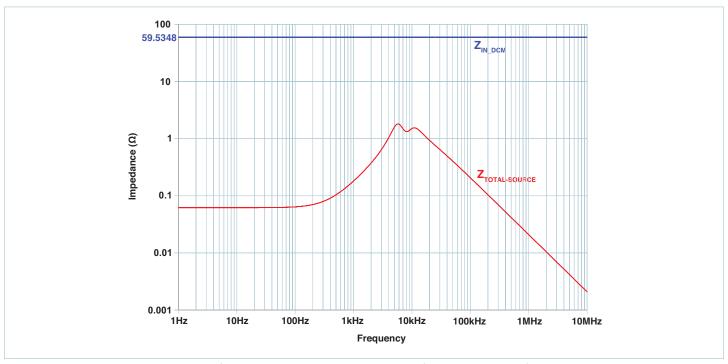

Figure 2.9 shows the source output impedance and the input impedance of the DCM, this clearly shows that the source output impedance is well damped. Since there is a large separation between the source output impedance and the input impedance of the DCM, no interaction is expected.

Another approach for reducing the effect of source impedance is adding a well damped input filter. Additional advantages of using an input filter are that it attenuates the conducted electromagnetic interference (EMI) and it provides input voltage noise rejection. Input filters are discussed in detail in the next section of the design guide. The simulations shown in Figure 2.10 include the input filter. The impedance simulation results illustrated in Figure 2.11 shows a large separation between the total output impedance (Z<sub>TOTAL-SOURCE</sub>) and the input impedance of the DCM; therefore, no interaction is expected.

Figure 2.8 — Example source and load subsystems with decoupling capacitor

Figure 2.9 — Output impedance of the source and the input impedance of the DCM, with a decoupling capacitor

Figure 2.10 — Example source and load subsystems with an input filter

Figure 2.11 — Output impedance of the source and the input impedance of the DCM, with an input filter

# Stability Analysis of a Multiple Converter System

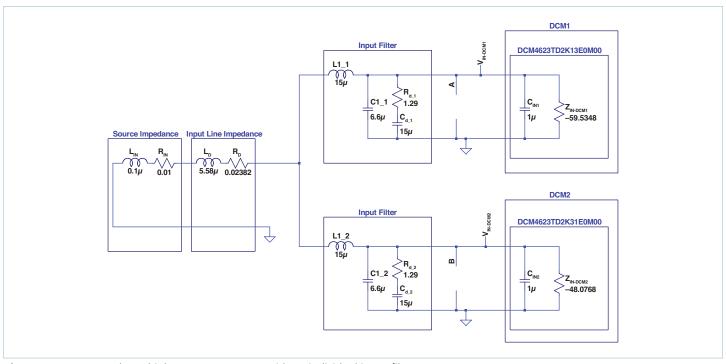

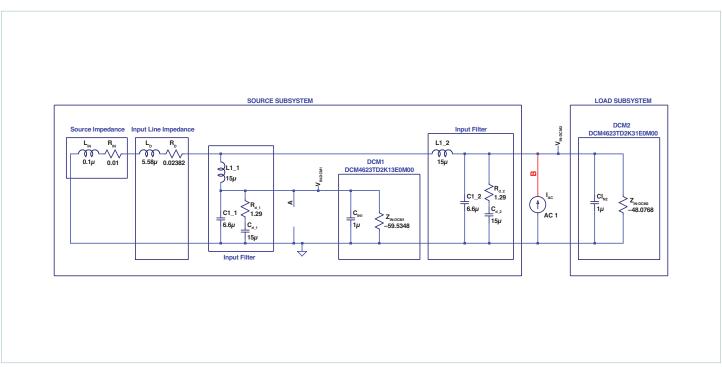

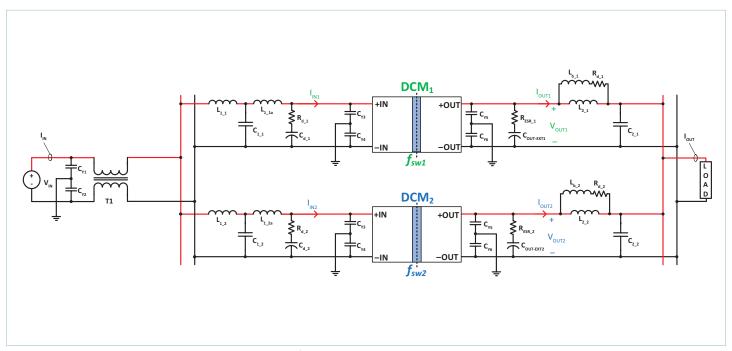

To analyze the stability of a multiple converter system, which is shown in Figure 2.2 (b), a simulation model is created in spice. The simulation model, shown in Figure 2.12 consists of a common source and line impedances connected to a DC bus and multiple

DCMs supplying the independent loads. DCM1 has a constant output power of 400W and DCM2 has a constant output power of 500W. The corresponding input power consumed by DCM1 and DCM2, including the losses is 430W, 533W, respectively. By using the Equation 2.1, the negative incremental input impedances  $Z_{\text{IN-DCM1}}$  and  $Z_{\text{IN-DCM2}}$  are calculated.

Figure 2.12 — Example multiple converter system with an individual input filter

Figure 2.13 — Equivalent source viewed from node A, multiple converter system separated into source and load subsystems

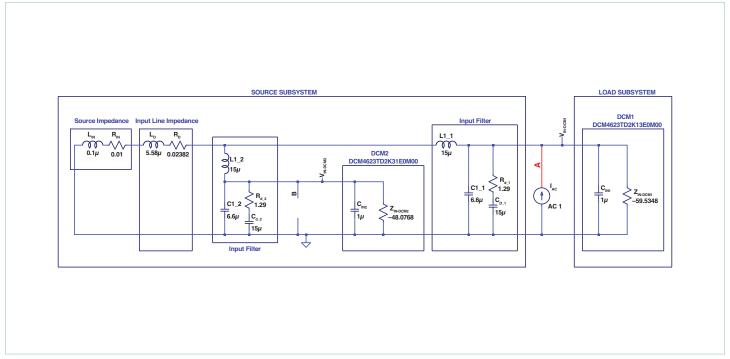

Figure 2.12 is redrawn to represent the complex multiple converter system in a much simpler way by separating into the source and load subsystems. The equivalent circuit is depicted in Figure 2.13 and shows an equivalent source ( $Z_{TOTAL_1-SOURCE}$ ) viewed from node A. The shunt branch consisting of  $L_{1.2}$ ,  $C_{1.2}$ ,  $R_{d.2}$ ,  $C_{d.2}$ ,  $C_{IN2}$  and  $Z_{IN-DCM2}$  is the impedance of DCM2 and its input filter viewed from

the DC bus. The simulation results shown in Figure 2.14 are the comparison of the input impedance of the DCM1 ( $Z_{\text{IN-DCM1}}$ ) and the total output impedance of the source ( $Z_{\text{TOTAL\_1-SOURCE}}$ ) viewed from node A. The results clearly show that the impedances are well separated and no interaction is expected over the frequency range of interest.

Figure 2.14 — Total output impedance of the source and the input impedance of the DCM1 viewed from node A

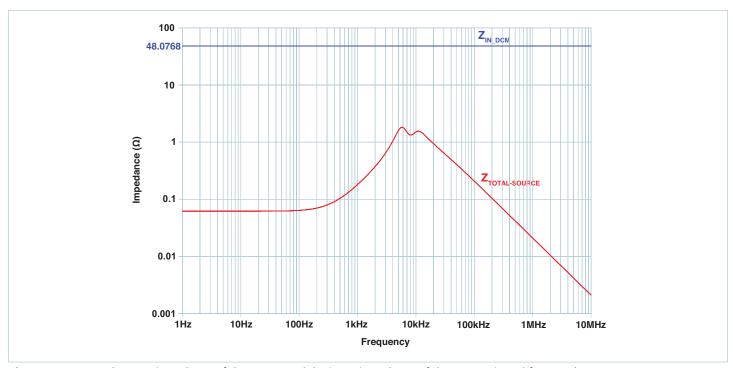

Figure 2.12 is redrawn in similar fashion as explained earlier, when viewed from the node B. The circuit shown in Figure 2.15 is an equivalent source ( $Z_{TOTAL\_2-SOURCE}$ ) viewed from node B. The shunt branch consisting of  $L_1$ ,  $C_{1-1}$ ,  $R_{d-1}$ ,  $C_{d-1}$ ,  $C_{IN1}$  and  $Z_{IN-DCM1}$  is the impedance of DCM1 and its input filter viewed from the DC bus. The simulation results, shown in Figure 2.15, clearly show that

the input impedance of the DCM2 ( $Z_{\text{IN-DCM2}}$ ) and the total output impedance of the source ( $Z_{\text{TOTAL\_2-SOURCE}}$ ) viewed from node B are well separated and no interaction is expected over the frequency range of interest. Therefore, no stability problems are expected in the multiple converter system.

Figure 2.15 — Equivalent source viewed from node B, multiple converter system separated into source and load subsystems

Figure 2.16 — Total output impedance of the source and the input impedance of the DCM2 viewed from node B

#### Input Filter Design and Simulation

#### Introduction

Switching power converters, including the DCM, generate noise currents at the switching frequency and its higher-order harmonics. The noise currents are of two types, common mode and differential mode and will propagate from the DCM back to the power source along the interconnecting conductors.

This noise may interfere with the power source operation and other systems sharing the same connection. Therefore, an input filter is often used between the power source and the switching converter to lower the conducted electromagnetic interference (EMI) and to provide input voltage noise rejection.

# **Differential-Mode Input Filter Design and Simulation**

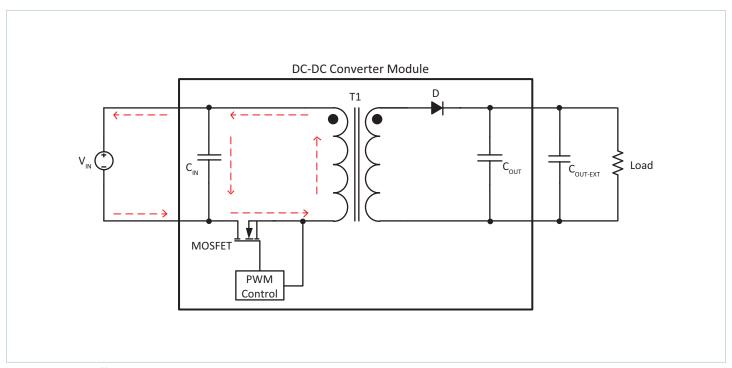

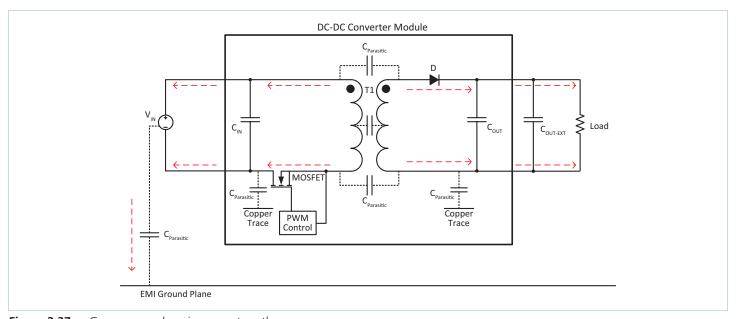

The differential-mode noise currents are result of normal operation of the circuit. The differential mode noise current path of a representative switching converter and the power source is shown in Figure 2.17.

**Figure 2.17** — Differential-mode noise currents path

# **Problems Associated with Addition of Input Filters:**

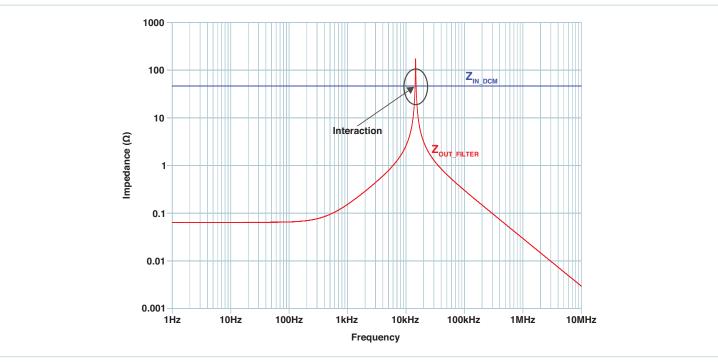

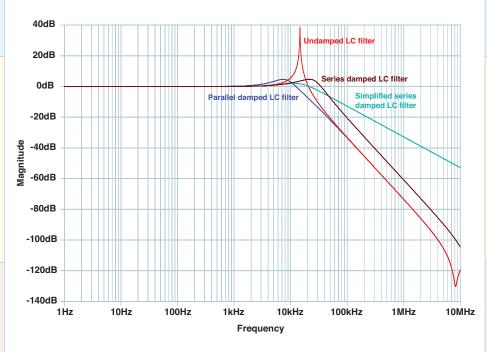

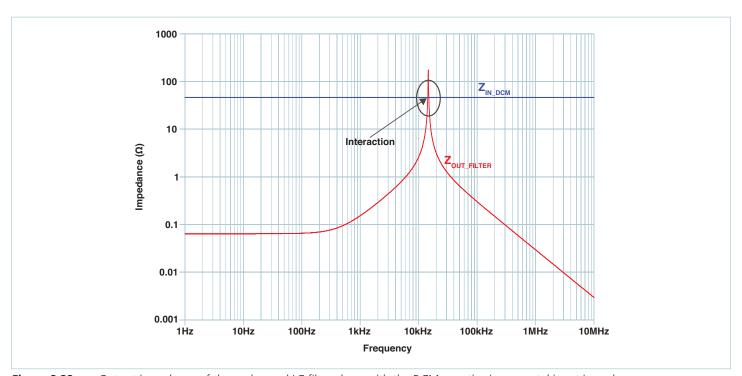

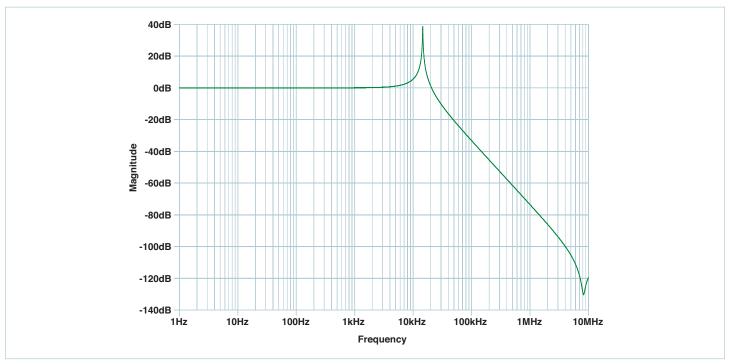

Introducing a filter at the input of a DCM without considering its impact on the switching converter dynamics can lead to system-level stability issues. The DCM, as a feedback controlled switching converter, behaves as a constant power load at the input terminals; the DCM presents a negative incremental impedance at its input terminals, plotted in blue in Figure 2.18. The output impedance of an example undamped input filter is also plotted in red in Figure 2.18. The interaction between the input filter's

output impedance and the DCM input impedance will often result in control loop instability of the DCM and degradation of dynamic performance. This, in turn, will cause large oscillations in the input voltage and output voltage during start up, load steps, and other transient events. These issues can be eliminated by appropriately damping the input filter. Various filter damping techniques are discussed in this section. Further details on switching converter system stability analysis are located in the section on source impedance and its effects on system stability.

Figure 2.18 — Filter output impedance interaction with DCM input impedance

#### **Input Filter Design**

Before diving into the design of the input filter, the designer must gather information on the following:

- Identify the noise spectrum of the DCM from the actual measurements or from the data sheet of the DCM.

- 2. Identify the operating point and plot the input impedance of the DCM using spice simulation tool. For mathematical analysis, please refer to the the section on source impedance and its effects on system stability.

- **3.** Identify the filtering requirements.

- **4.** Select an appropriate filter network to meet the filtering requirements.

Commonly used differential mode input filtering network topologies for switching power converters are as follows:

- 1. Undamped LC filter

- 2. Parallel damping

- a. Simplified parallel damping

- 3. Series damping

- 4. Simplified series damping

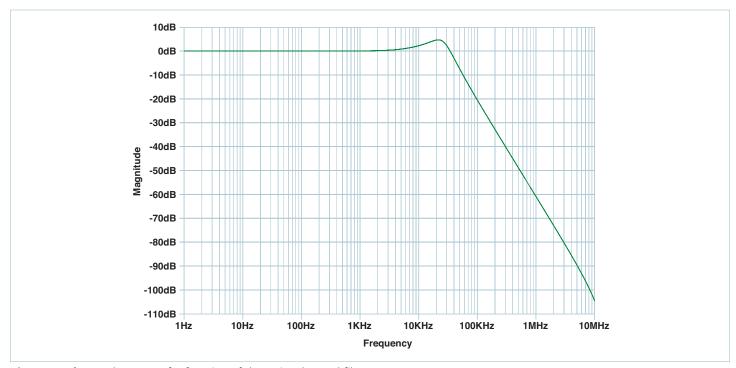

In order to see the differences in the performance of above mentioned filter network topologies, an example of designing an input filter network for DCM4623TD2K31E0T00 (160 - 420V $_{\rm IN}$ , 28V $_{\rm OUT}$ , 500W) using the spice simulation tool is considered. The aim of this filter design is to obtain at least  $-40 \, \rm dB$  attenuation at the switching frequency (1MHz).

To achieve this aim, an undamped LC filter network topology is initially used. This topology is a second order system that provides a roll-off of –40dB/decade. Therefore, as a rule of thumb, the cutoff frequency must be at least ten times lower than the converter switching frequency.

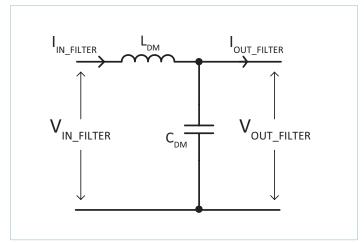

# **Undamped LC filter**

# Parallel-damped LC filter

# Series-damped LC filter

# Simplified series-damped LC filter

# **Frequency Response Plot** (Voltage / Current Transfer Function)

**Filter Topology & Common Notes**

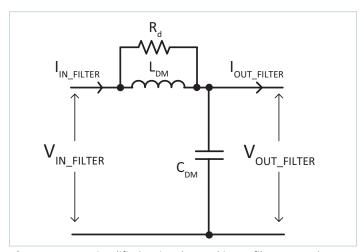

According to the duality property, the voltage transfer function viewed from the input side is same as the current transfer function viewed from the output side.

$$TF = \frac{V_{OUT\_FILTER}}{V_{IN\_FILTER}} = \frac{I_{IN\_FILTER}}{I_{OUT\_FILTER}}$$

Cut-off frequency:

$$f_c = \frac{1}{2\pi\sqrt{L_{DM}C_{DM}}} (Hz)^{[a]}$$

Where LDM = Filter Inductor CDM = Filter Capacitor

- The cut-off frequency must be below the crossover frequency of the converter.

- At resonance  $\omega L_{DM} = 1 / \omega C_{DM}$ , characteristic impedance:

$$R_{\scriptscriptstyle O} = \sqrt{\frac{L_{\scriptscriptstyle DM}}{C_{\scriptscriptstyle DM}}}$$

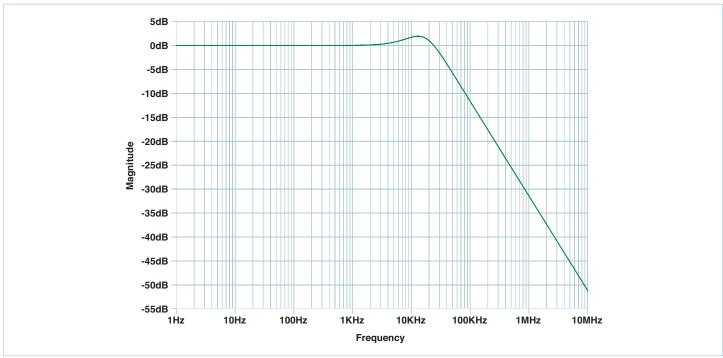

$\bullet$  All the topologies are a second order system that provides a roll-off of –40dB / decade ([a] See specific notes of simplified series-damped LC filter).

• Q-factor of ideal components in spice models at the resonant frequency is infinite.

**Equations and Notes**

• Damping can be achieved using series resistors as shown below:

# **Damped LC filter**

- Least component count.

- Size of the filter is small.

- Cost is lower.

• A damping resistor in series with inductor L<sub>DM</sub> degrades the efficiency and a damping resistor in series with capacitor C<sub>DM</sub> degrades the attenuation characteristics

of the filter..

• Peaking at resonant frequency.

Disadvantages

The value of blocking capacitor:  $C_d = nC_{DM}$ The value of peak output impedance:

$$|Z_{OUT\text{-}FLTER}| = R_O \frac{\sqrt{2(2+n)}}{n}$$

The value of damping resistance:

$$R_d(optimum) = R_O \sqrt{\frac{(2+n) \cdot (4+3n)}{2n^2(4+n)}}$$

• At the resonant / cutoff frequency, the capacitor C<sub>d</sub> must have lower impedance than R<sub>d</sub> and a larger impedance than the filter

**Advantages**

• R<sub>d</sub> – C<sub>d</sub> parallel branch can be replaced with a higher ESR value capacitor type (aluminum electrolytic or tantalum), shown below:

- Require a high value blocking capacitance C<sub>d</sub>.

- Size and cost of the filter increase.

The value of blocking inductor:  $L_b = nL_{DM}$ The value of peak output impedance:

$$|Z_{OUT\text{-}FLTER}| = R_O \sqrt{2n(1+2n)}$$

The value of damping resistance:

$$R_d(optimum) = R_O \sqrt{\frac{n(3+4n)(1+2n)}{2(1+4n)}}$$

- The inductor L<sub>b</sub> must have an impedance magnitude that is sufficiently smaller than R<sub>d</sub> at the filter resonant frequency.

- Size of the filter is small compared to parallel-damped LC filter.

- High-frequency attenuation is degraded.

system, ideally this should provide a roll-off of -40dB / decade, however, due to high-frequency zero  $(f_z = R_d / (2\pi L_{DM}))$  the roll-off is -20dB / decade.

[b] Simplified series-damped LC filter is a second order • Low component count compared to parallel-damped and series-damped filters.

• High-frequency attenuation is degraded.

#### Design Steps:

- 1. Select the cut-off frequency below the crossover frequency (20kHz) of the DCM.

- 2. Choose the inductor L<sub>DM</sub> based on maximum input current, calculate C<sub>DM</sub> using Equation [a] above.

- 3. Select appropriate filter network and calculate the component values based on equations and notes.

- a. Assume peak output impedance | Z<sub>OUT-FILTER</sub>| at least ten times lower than input impedance of switching converter

#### Component Selection:

- $\textbf{1. Choose the self-resonating frequency (SRF) of inductor ($L_{DM}$) and capacitor ($C_{DM}$) to be higher than the switching frequency or the converter.}$

- 2. Use the multiple ceramic capacitors in parallel for C<sub>DM</sub>. This, in turn, will effectively attenuates the high-frequency noise.

- 3. Use low-Q devices, designed for filtering.

$DCM^{TM}$

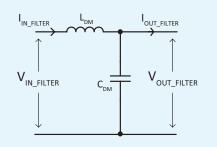

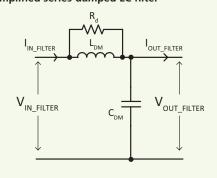

# 1. Undamped LC Filter Network

The undamped input filter circuit shown in Figure 2.19 is a second-order low-pass filter circuit that provides a high-frequency roll-off of –40dB / decade. The resonant frequency of this filter, also known as the cutoff frequency when considering the voltage response is given by the following expression:

$$f_c = \frac{1}{2\pi\sqrt{L_{DM}C_{DM}}} (Hz)$$

The peak filter output impedance will occur at this same frequency  $f_{\rm c}$ . The Q-factor for ideal components at the resonant frequency is infinite. However, intrinsic parasitic resistances of the filtering components will limit the peak response. Nonetheless, the output impedance of the undamped LC filter is very large near the resonant frequency. At the resonance condition  $\omega L = 1 / \omega C$ , the characteristic impedance,  $R_0$  is given by:

$$R_O = \sqrt{\frac{L_{DM}}{C_{DM}}}$$

Figure 2.19 — Undamped LC filter

# **Damping the Filter**

Parasitic resistances of the inductor and capacitor will provide damping, but may not be sufficient to reduce the resonance peak to acceptable limits. One solution is to provide an additional damping, can be achieved by adding an external resistor in series with the inductor and capacitor, shown in Figure 2.20. However, a damping resistor in series with the inductor will increase the losses and a damping resistor in series with the capacitor will degrade the attenuation characteristics. Therefore, series- / parallel-damping techniques are preferred over the undamped LC filter.

Figure 2.20 — Damping using series resistors

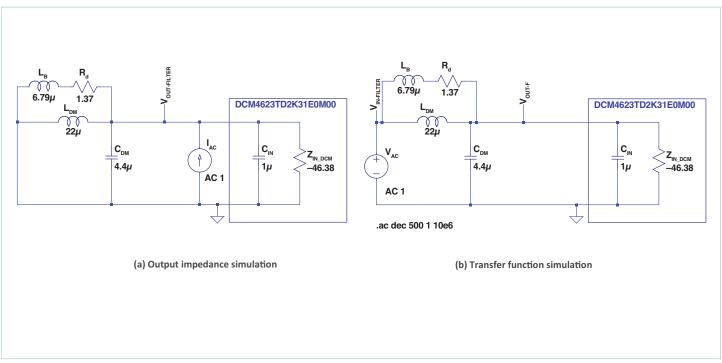

## Design Example

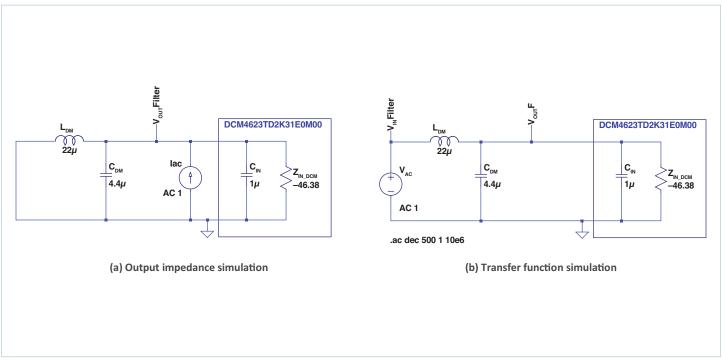

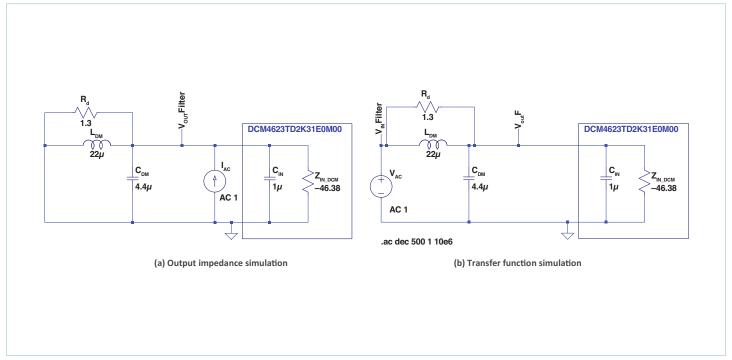

The DCM4623TD2K31E0T00 ( $160-420V_{IN}$ ,  $28V_{OUT}$ , 500W) with an undamped LC input filter is simulated in spice, as shown in Figure 2.21. To measure the output impedance of the filter, independent input voltage source ( $V_{DC}$ ) is shorted and an AC current is injected at the output terminals of the filter as in 2.21(a). Filter attenuation characteristics can be obtained by injecting an AC voltage signal at the input terminals of the filter as shown in 2.21(b).

In this design example, the cutoff frequency  $f_{\rm C}$  of the filter is chosen as 15kHz. By choosing the value of inductor  $L_{\rm DM}$  = 22 $\mu$ H, the value of  $C_{\rm DM}$  is calculated as follows.

$$15kHz = \frac{1}{2\pi\sqrt{22\mu H \cdot C_{DM}}}$$

$$C_{DM} = 5.12 \mu F$$

**NOTE:** The internal capacitance of the DCM (C<sub>INT\_DCM</sub>) is considered in these simulations (for the value of internal capacitance, please refer to the Figure "Effective internal input capacitance vs. applied voltage" in the DCM4623TD2K31E0T00 data sheet copied in Figure 2.7).

Figure 2.21 — Undamped LC filter network along with the DCM negative input impedance

Figure 2.22a — Output impedance of the undamped LC filter along with the DCM negative incremental input impedance

Figure 2.22b — Voltage transfer function of the undamped LC filter

According to the frequency response plots, shown in Figure 2.22b, the filter attenuation target is met. However, at the resonance (shown in Figure 2.22a), the output impedance of the input filter is interacting with the input impedance of the DCM. In this case, there could be potential stability issues leading to large oscillations in the input voltage. In order to avoid the instability, the peak magnitude of the output impedance must be at least ten times below the input impedance of the DCM; this can be achieved by using a proper damping scheme.

**Note:** Since further discussed input filter network topologies are based on the undamped LC filter network, the resonant frequency  $f_{\rm c}$  of damping filter networks and roll-off will remain same.

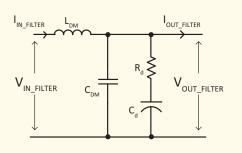

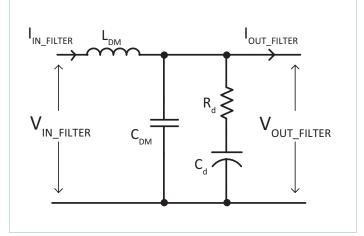

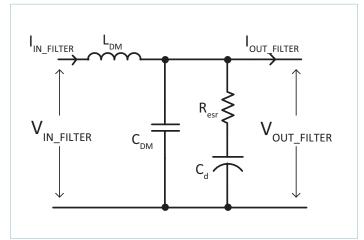

#### 2. Parallel-Damped Filter Network

A parallel-damped filter is obtained by connecting a parallel branch of a blocking capacitor ( $C_d$ ) in series with the damping resistor ( $R_d$ ) to the undamped LC filter network as shown in Figure 2.23.

The resistance  $R_d$  reduces the output peak impedance of the filter at the cutoff frequency. The capacitor  $C_d$  blocks the DC component of the input voltage, preventing excessive power dissipation from  $R_d$ . At the resonant / cutoff frequency, the capacitor  $C_d$  must have lower impedance than  $R_d$  and a larger impedance than the filter capacitor  $C_{DM}$  so as to not affect the cutoff point of the main LC filter. Therefore, the value of the blocking capacitor must be chosen to be larger in comparison to capacitor  $C_{DM}$ . The value of blocking capacitor is given by the expression  $C_d = nC_{DM}$ .

**Figure 2.23** — Damping using series resistors

To determine the value of n and an optimum value of  $R_d$ , the value of the peak output impedance of the filter must be chosen.

The value of peak output impedance for an optimum design is given by:

$$|Z_{OUT\text{-}FLTER}| = R_O \frac{\sqrt{2(2+n)}}{n}$$

Where  $R_O = \sqrt{(L_{DM}/C_{DM})}$

The value of damping resistance that leads to the optimum damping is given by:

$$R_d(optimum) = R_O \sqrt{\frac{(2+n) \cdot (4+3n)}{2n^2(4+n)}}$$

# Design Example

The same filter requirements as mentioned earlier in undamped LC filter design example are again considered. In addition, the filter is designed to meet the peak output impedance ( $|Z_{Out\text{-}FLTER}|$ ) of  $2\Omega$ , which is more than ten times lower than the input impedance of the DCM.

$$R_o = \sqrt{\frac{22\mu H}{5.4\mu F}} = 2.0$$

$$2\Omega = 2.0 \, \frac{\sqrt{2(2+n)}}{n}$$

$$n = 3.23$$

Therefore,

$R_d$  (optimum)=1.37,

$$C_d = 3.23(5.4\mu F) = 17.44\mu F$$

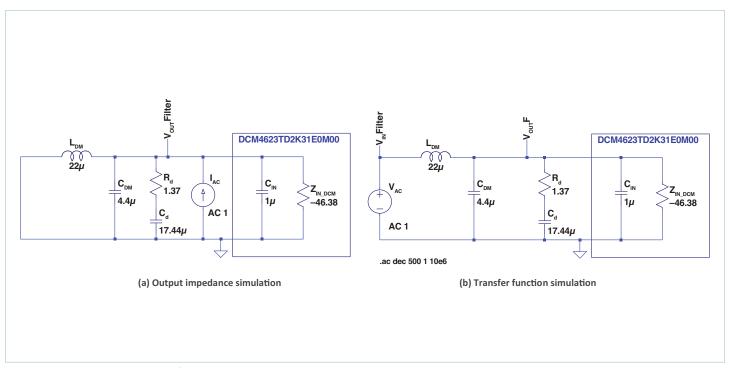

Simulation of the filter has been carried out in spice to verify the filter attenuation characteristics, as shown in Figure 2.24.

Figure 2.24 — Parallel-damping filter network along with the DCM negative input impedance

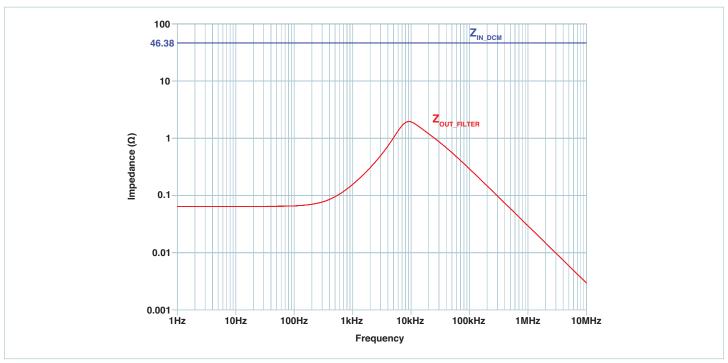

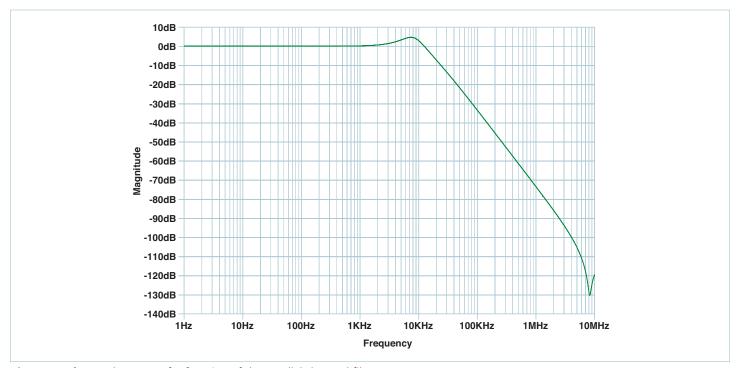

From the frequency response plots, as shown in Figure 2.25b, it can be observed that the output impedance of the filter is more than ten times below the DCM input impedance. The filter has an attenuation characteristics of –70dB at 1MHz with a roll-off of –40dB /decade.

Figure 2.25a — Output impedance of the parallel-damped filter along with the DCM negative input impedance

Figure 2.25b — Voltage transfer function of the parallel-damped filter

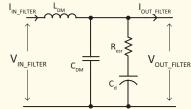

# 2a. Simplified Parallel-Damping Network

A simplified version of the parallel-damping network is shown in Figure 2.26. In order to reduce the component count of the filter shown in Figure 2.23, blocking capacitor  $C_d$  and series resistor  $R_d$  can be replaced with a capacitor that has higher value of effective series resistance (ESR). Usually aluminum electrolytic or tantalum capacitor types provide higher ESR. Therefore, the component count is reduced.

Figure 2.26 — Simplified parallel-damped input filter network

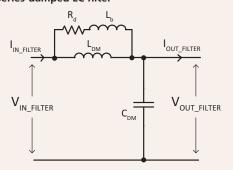

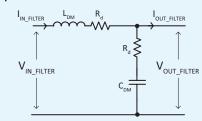

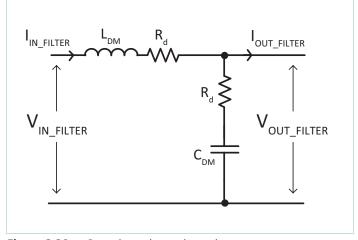

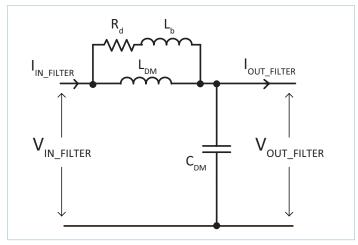

#### 3. Series-Damped Filter Network

A series-damped filter is obtained by connecting a parallel branch of blocking inductor ( $L_b$ ) in series with the damping resistor ( $R_d$ ) with the filter inductor ( $L_{DM}$ ) to the undamped LC filter network as shown in Figure 2.27. The inductor  $L_b$  causes the filter to exhibit a two-pole attenuation characteristic at high frequency.

Figure 2.27 — Series-damped input filter network

The resistance  $R_d$  reduces the output peak impedance of the filter at the resonant frequency. The inductor  $L_b$  on the other hand blocks the DC component of the input voltage which prevents power dissipation on  $R_d$ . However, in order to allow  $R_d$  to damp the filter, the inductor  $L_b$  must have an impedance magnitude that is sufficiently smaller than  $R_d$  at the filter resonant frequency.

Therefore, the value of the blocking inductor  $L_b$  must be chosen to be smaller as in comparison to filter inductor  $L_{DM}$ . The value of the blocking inductor is given by the expression  $L_b = nL_{DM}$ .

The value of peak output impedance for an optimum design is given by:

$$|Z_{OUT\text{-}FLTER}| = R_O \sqrt{2n(1+2n)}$$

Where

$$R_{\scriptscriptstyle O} = \sqrt{(L_{\scriptscriptstyle DM}/C_{\scriptscriptstyle DM}})$$

The value of damping resistance that leads to the optimum damping is given by:

$$R_d(optimum) = R_O \sqrt{\frac{n(3+4n)(1+2n)}{2(1+4n)}}$$

# Design Example

Again, the attenuation characteristics similar to that of design example of undamped LC filter are considered. To determine the value of n and an optimum value of  $R_d$ , the value of the peak output impedance ( $|Z_{OUT-FLTER}|$ ) of the filter is assumed to be  $2\Omega$ , which is ten times lower than the input impedance of the DCM.

$$R_o = \sqrt{\frac{22\mu H}{5.4\mu F}} = 2.0$$

$$2\Omega = 2.0\sqrt{2n(1+2n)}$$

$$n = 0.309$$

Therefore,

$$R_{d-optimum} = 1.37$$

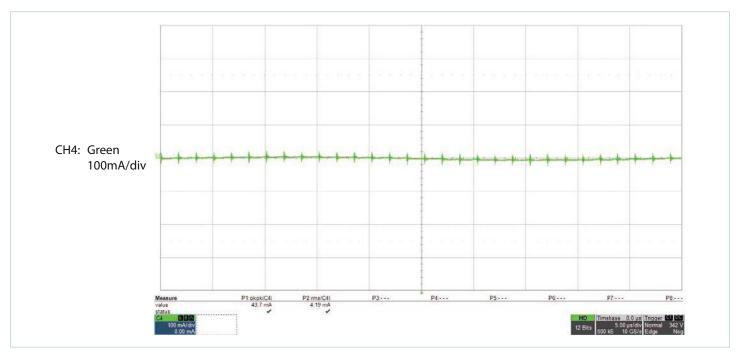

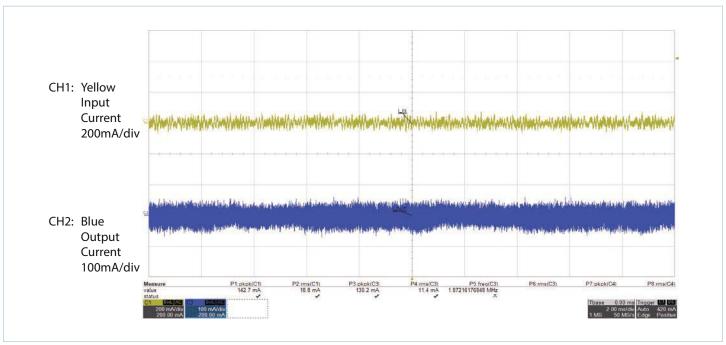

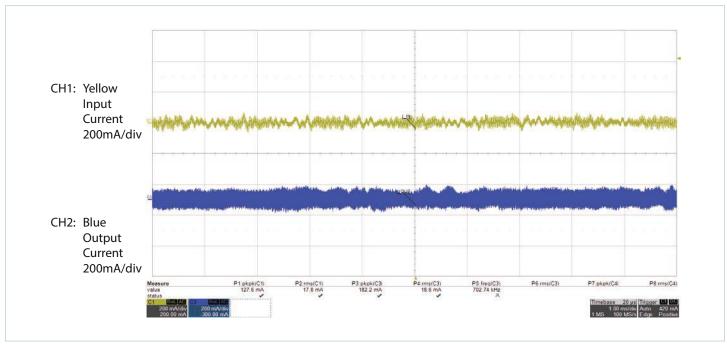

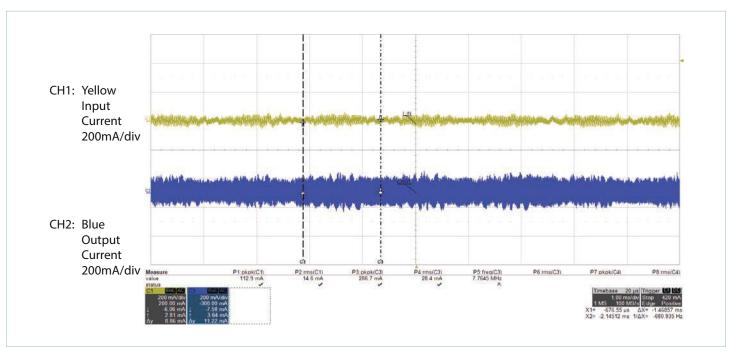

,