New technique increases chip yield from semiconductor wafer

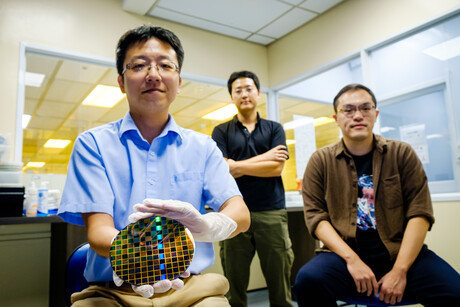

Scientists from Nanyang Technological University, Singapore (NTU Singapore) and the Korea Institute of Machinery & Materials (KIMM) have developed a technique to create a highly uniform and scalable semiconductor wafer, paving the way for higher chip yield and more cost-efficient semiconductors. Their results have been published in the journal ACS Nano.

Semiconductor chips commonly found in smartphones and computers are difficult and complex to make, requiring highly advanced machines and special environments to manufacture. Their fabrication is typically done on silicon wafers and then diced into the small chips that are used in devices, but the process is imperfect and not all chips from the same wafer operate as desired. These defective chips are discarded, lowering semiconductor yield while increasing production cost.

The ability to produce uniform wafers at the desired thickness is the most important factor in ensuring that every chip fabricated on the same wafer performs correctly. Nanotransfer-based printing — a process that uses a polymer mould to print metal onto a substrate through pressure, or ‘stamping’ — has gained traction in recent years as a promising technology for its simplicity, relative cost-effectiveness and high throughput; however, the technique uses a chemical adhesive layer which causes surface defects and performance degradation when printed at scale, as well as human health hazards. For these reasons, mass adoption of the technology and consequent chip application in devices has been limited.

The research team from NTU and KIMM reported that their chemical-free printing technique, when combined with metal-assisted chemical etching — a method used to enhance the contrast on surfaces to make nanostructures visible — resulted in semiconductor wafers with nanowires (nanostructures in cylindrical form) that were highly uniform and scalable. The semiconductor also demonstrated better performance when compared with current chips in the market. Moreover, the fabrication method is fast and leads to high chip yield.

The nanotransfer printing technique is accomplished by transferring gold (Au) nanostructure layers onto a silicon (Si) substrate at low temperature (160°C) to form a highly uniform wafer with nanowires that can be controlled to the desired thickness during fabrication. The chemical-free printing technique works by triggering direct chemisorption of the thin metal films under heat — a chemical reaction that creates a strong bond between a substrate surface and the substance that is adsorbed. This industrial-compatible technique allows a wafer to be fabricated quickly and uniformly at scale (from nanometres to inches). At the same time, the fabricated wafer is almost defect-free, meaning that few chips are discarded due to poor performance.

In lab tests, the research team was able to achieve more than 99% yield transfer of a 20 nm-thick Au film onto a 6″ Si wafer. Results showed the printed layer remained intact with minimal bending during etching — a process that commonly causes layers to separate — demonstrating the uniformity and stability of the technique. Furthermore, when 100 light sensors, known as photodetectors, were fabricated into the 6″ wafer, excellent uniformity of performance was achieved, underlining the potential for the technique to be used in commercial mass production.

Co-lead researcher Assistant Professor Kim Munho, from NTU, said the uniformity, scalability and stability of the team’s technique overcomes the main bottleneck present in existing nanotransfer printing methods. And while the printable wafer size was limited to the laboratory set-up, the team believes their technique can easily be scaled up for use on a 12″ wafer — the mainstream wafer size in the current production lines of semiconductor chipmakers like Samsung, Intel and GlobalFoundries.

“The technique devised by the research team from NTU and KIMM has proven to be effective in creating wafer with excellent uniformity, which translates into fewer defective semiconductor chips,” Asst Prof Kim said.

“The reality of global chip supply is its vulnerability to many external factors, including shortage of materials and unexpected events like the supply chain disruptions caused by the COVID-19 pandemic. Our newly developed method thus has potential to relieve the tension on the global chip supply in future by increasing chip yield. Moreover, chip makers may also enjoy greater cost-efficiency with higher yields.”

Co-lead author Dr Jeong Jun-Ho, from KIMM, added, “The technique developed by the NTU–KIMM team is a new concept of low-cost mass production technology for highly uniform and scalable semiconductor nanostructures, which can be applied to the mass production of nanophotonics, high-performance nano solar cells, next-generation secondary batteries and others.”

The research team has filed for patents in Korea and Singapore for the technique they developed. The team is aiming to scale up their technique with an industrial partner for commercialisation within the next few years.

Please follow us and share on Twitter and Facebook. You can also subscribe for FREE to our weekly newsletter and bimonthly magazine.

Fungi-based semiconductors for flexible electronics

Researchers have harnessed fungi-derived materials to create flexible semiconductors, advancing...

Novel transistor enhances sensing in liquids

Researchers have developed a novel transistor sensor that maintains high accuracy in liquids,...

Photonic AI chip processes data at the speed of light

Aussie researchers have built an ultra-compact nanophotonic AI chip that performs neural network...